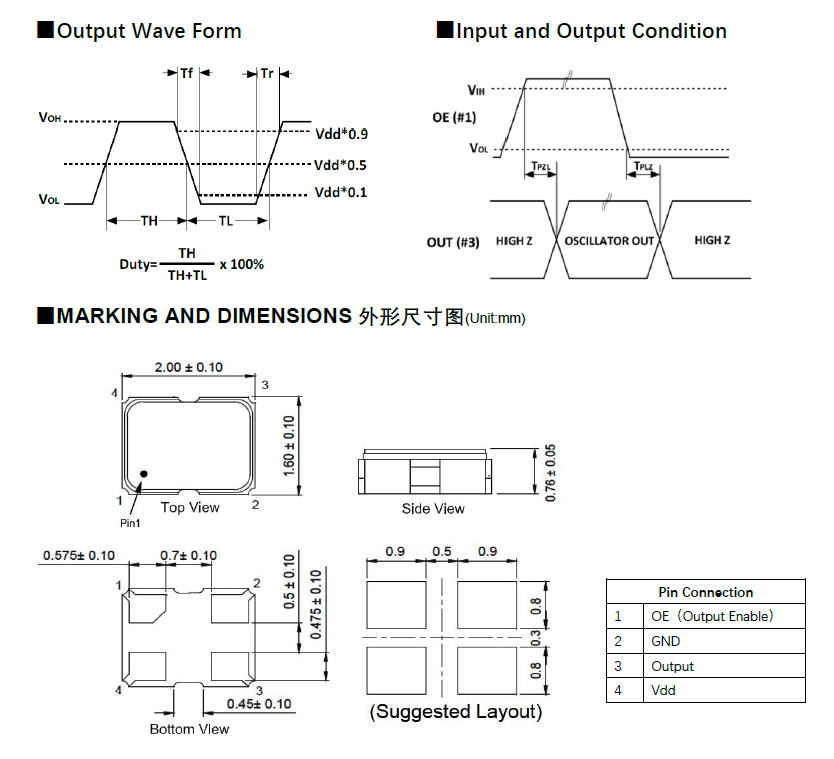

CMOS Output Wave Form

关于有源晶振不同电压的峰峰值,晶诺威科技解释如下:

简单来说:供电电压越高,通常输出峰峰值也越高,但不同逻辑类型的输出特性决定了其峰峰值与供电电压的关系。以下是不同电压和不同输出逻辑类型下有源晶振峰峰值的详细说明和典型值参考:

核心决定因素:输出逻辑类型

有源晶振的输出信号本质上是一个方波(或正弦波,取决于类型),其电气特性由其“输出逻辑”规范决定。

1、 LVCMOS输出

这是最常见的有源晶振类型。其输出为方波,峰峰值非常接近供电电压Vcc。

典型关系:Vpp≈Vcc

示例:

3.3V供电:输出峰峰值通常为3.0V~3.3V。

5.0V供电:输出峰峰值通常为4.5V~5.0V。

1.8V供电:输出峰峰值通常为1.7V~1.8V。

特点:驱动能力强,上升/下降沿陡峭,频谱丰富(谐波多),可能产生更多噪声。

2、 HCMOS/TTL输出

早期或兼容5V系统的标准,现在较少见。其高电平电压(Voh)通常比Vcc低约1V。

典型关系:Vpp≈Vcc-1V,但具体看规格书。

示例:5V供电时,峰峰值可能在4V左右。

3、 Clipped Sine Wave/削峰正弦波输出

这种输出不是方波,而是近似正弦波,但顶部和底部被“削平”。其峰峰值通常小于Vcc,且与负载电阻(如50Ω)有关。

典型关系:Vpp在0.8V到Vcc之间,常见值为0.8Vpp或1.0Vpp,与Vcc关系不大。

特点:谐波分量少,电磁干扰小,常用于射频、高速SerDes时钟等对信号纯净度要求高的场合。

4、 LVDS输出

低压差分信号,由一对差分线(正负)传输。其峰峰值是差分电压,且与Vcc无关。

典型值:差分峰峰值Vpp_diff通常为250mV~800mV(最常见350mV)。单端对地电压约为这个值的一半。

特点:抗干扰能力强,速度极高,功耗相对低,用于高速传输。

5、 PECL输出

正发射极耦合逻辑,也是一种差分输出。其输出电压与Vcc强相关。

典型关系:Voh≈Vcc-0.9V,Vol≈Vcc-1.7V。因此,单端峰峰值Vpp_se≈0.8V,

差分峰峰值Vpp_diff≈1.6V。

特点:速度极高,功耗大,需要直流偏置和终端匹配。

总结表格(典型值参考)

重要注意事项

1、 以规格书为准:以上均为典型值。最准确的参数必须查阅晶振厂商提供的Datasheet(数据手册)。手册中会明确给出Voh(输出高电平)和Vol(输出低电平),峰峰值即Voh-Vol。

2、 负载影响:输出电压峰峰值与负载电容/电阻直接相关。例如,LVCMOS驱动过大的容性负载会导致边沿变缓,实际测得的峰峰值可能降低。削峰正弦波的输出电压由内部电阻和外部负载电阻分压决定。

3、 测量工具:使用示波器测量时,请确保带宽足够(至少是晶振频率的3-5倍),并使用正确的探头(如测量差分信号需用差分探头或使用示波器数学函数计算通道差值)。

4、电压匹配:选择晶振时,不仅要看电压峰峰值,更要确保其逻辑电平与接收芯片的输入电平要求兼容。例如,给一个1.8V的LVCMOS输入引脚提供3.3V的LVCMOS时钟,可能会损坏芯片。

拓展阅读:晶振的Output Level(输出电平)

晶振的Output Level(输出电平),简单来说,就是晶振在正常工作时,输出引脚能产生的电信号的幅度或电压范围。

你可以把它理解为晶振输出信号的“音量”大小。它通常用以下两种方式描述:

波形与幅度:比如是削峰正弦波还是方波。方波的电平会接近其供电电压(如3.3V),而正弦波的幅度通常较低。

逻辑电平标准:常见的有LVCMOS(低压CMOS)、LVPECL(低压正发射极耦合逻辑)、LVDS(低压差分信号)等。它们各自有特定的电压摆幅(如LVDS的幅度约为350mV)。

这个参数的重要性在于兼容性。如果输出电平过低,后端芯片可能无法识别信号(导致无声或故障);如果过高,则可能损坏接收电路。同时,它也与功耗相关,通常电平越高、频率越快,功耗也越大。