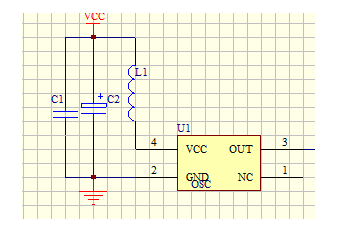

(有源晶振EMC标准电路)

在有源晶振EMC标准电路设计时,如果对EMC要求不高,可以去掉L1磁珠及C1负载电容,只保留电源输入端的去耦电容,取0.1uF即可,输出端保留输出电阻,约10Ω~27Ω。

具体操作如下:

1、电源端磁珠L1与电容C2、C3构成LC滤波电路。

2、信号输出端串联电阻是为了减小反射波,避免反射波叠加引起过冲。有时,不同批次的电路板特性可能存在差异,因此建议预留一个电阻位置便于调整电路板状态到最佳。如无必要串电阻,就用0Ω电阻连接。

补充说明:

- 可以减少谐波,有源晶体输出的是方波,这将引起谐波干扰,尤其是阻抗严重不匹配的情况下,加上电阻后,该电阻将与输入电容构成RC积分平滑电路,将方波转换为近似正弦波,虽然信号的完整性受到一定影响,但由于该信号还要经过后级放大、整形后才作为时钟信号,因此,性能并不受影响,该电阻的大小需要根据输入端的阻抗、输入等效电容,有源晶体的输出阻抗等因素选择。

- 可以进行阻抗匹配,减小回波干扰及导致的信号过冲。我们知道,只要阻抗不匹配,都会产生信号反射,即回波,有源晶体的输出阻抗通常都很低,一般在几百欧以下,而信号源的输入端在芯片内部结构上通常是运放的输入端,由芯片的内部电路与外部的无源晶振构成谐振电路。