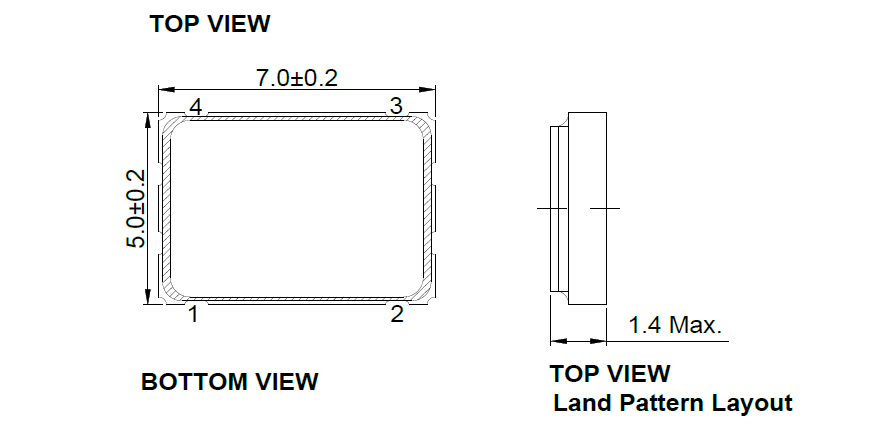

晶诺威科技产OSC7050有源晶振100MHz尺寸:

OSC7050有源晶振100MHz焊盘脚位说明如下:

(OSC7050有源晶振100MHz焊盘脚位说明)

OSC7050有源晶振100MHz规格参数介绍如下:

- Nominal Frequency :100.000000MHz

- Size: 7.0mm*5.0mm

- Power Voltage (±10%): +3.3V, +5V

- Output Waveform : C-MOS

- Operating Temperature:

-10 ~ +70℃

-40 ~ +85℃

-40 ~ +125℃

- Frequency Stability:

±20ppm (-10 ~ +70℃)

±25ppm(-40 ~ +85 ℃)

±100 ppm(-40 ~ +125℃)

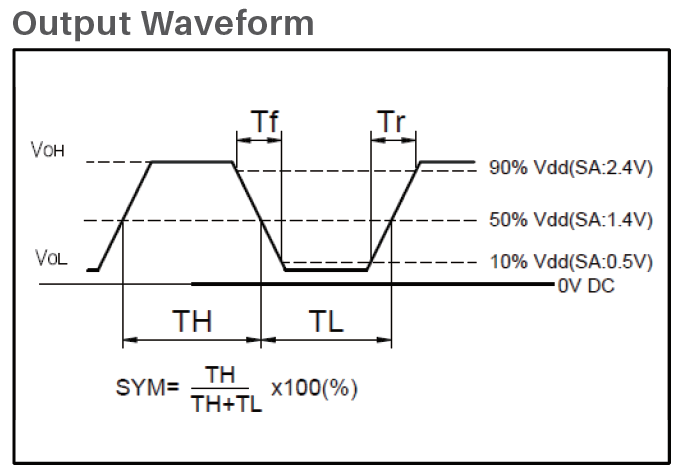

- Output Character: “0” Level 10%VDD Max. “1” Level 90%VDD Min

- Rise Time: (Tr) 10% ~ 90%VDD 10ns Max.

- Fall Time: (Tf) 90% ~ 10%VDD 10ns Max.

- Symmetry: 60/40 to 40/60 at 50%VDD

- Output Load(输出负载): 15pF,30pF

- Current Consumption: (Icc) 20 mA Max.

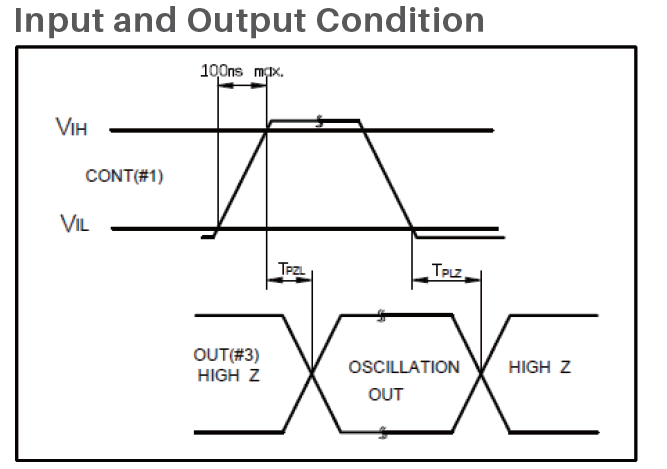

- Stand-by Current: (#1 pin = “ L” Level): (I_std) 10 uA Max.

- Start-up Time: 5 ms Max.

- Phase Jitter: 1ps Max. (F offset : 12KHz ~ 20MHz)

- Storage Temp.: -55 ℃ ~ +125 ℃

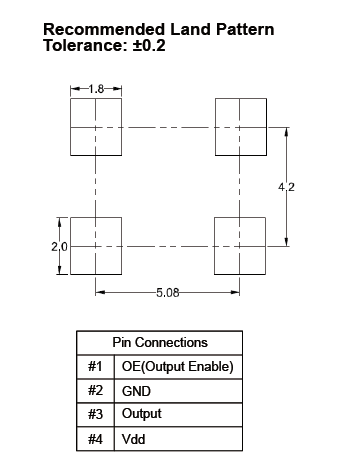

OSC7050有源晶振100MHz测试电路图:

OSC7050有源晶振100MHz输出波形:

OSC7050有源晶振100MHz输入输出条件:

拓展阅读:晶振的Output Level(输出电平)

晶振的Output Level(输出电平),简单来说,就是晶振在正常工作时,输出引脚能产生的电信号的幅度或电压范围。

你可以把它理解为晶振输出信号的“音量”大小。它通常用以下两种方式描述:

波形与幅度:比如是削峰正弦波还是方波。方波的电平会接近其供电电压(如3.3V),而正弦波的幅度通常较低。

逻辑电平标准:常见的有LVCMOS(低压CMOS)、LVPECL(低压正发射极耦合逻辑)、LVDS(低压差分信号)等。它们各自有特定的电压摆幅(如LVDS的幅度约为350mV)。

这个参数的重要性在于兼容性。如果输出电平过低,后端芯片可能无法识别信号(导致无声或故障);如果过高,则可能损坏接收电路。同时,它也与功耗相关,通常电平越高、频率越快,功耗也越大。