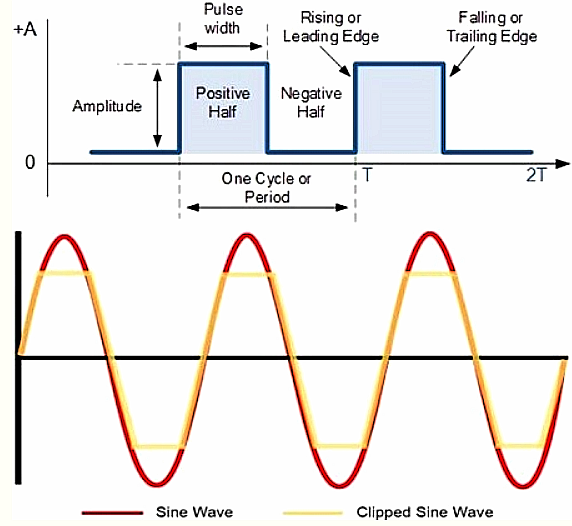

(晶振输出逻辑: 正弦波、削峰正弦波和方波)

晶振输出类型总体可分为三大类:正弦波输出、削峰正弦波输出和方波输出。

- 正弦波(Sine Wave)为普通无源晶振常见输出逻辑。

- 方波(Cmos)为常规有源晶振输出逻辑。

- 削峰正弦波(Clipped Sine Wave)为温补晶振(TCXO)常见输出逻辑。

CMOS (HCMOS和LVCMOS)是适合低频时钟(通常低于250MHz)的方波数字输出,可实现在时钟输出和芯片输入之间直接连接。在大多数情况下,可以使用低值串联电阻器来有效减少信号反馈并保持可靠的信号完整性。CMOS(HCMOS和LVCMOS)通常为普通有源晶振输出逻辑,包括压控晶振(VCXO)及压控温补晶振(VC-TCXO)等。

拓展阅读:差分晶振输出逻辑

PECL输出经常在高速时钟分配电路中使用,这是因为PECL具有很高的抗噪能力,能够在较长的线路长度上驱动高数据速率,并且由于电压摆幅较大而具有良好的抖动性能,但是PECL需要高功耗才能运行。

LVPECL为千兆位以太网和光纤通道的使用奠定了良好的基础。与LVDS相比,LVPECL可以提供更大的差分电压摆幅和稍低的电源效率。需要注意的是LVPECL的输出需要端接来发射电压。同样芯片中的差分电路可能具有不同的输入容差,因此确保正确端接以达到最佳性能是关键所在。

LVDS类似于LVPECL输出,但是LVDS的功耗较低,并且电压摆幅较小LVDS。通常用于满足时钟分配或背板收发器等高速数据传输需求。对于更高的数据速率通常首选HCSL、CML或LVPECL,但与LVDS相比,它们将需要更多的功耗。其它好处包括降低了对噪声的敏感性,并且易于在CMOS IC中实现。LVDS的缺点是与PECL相比其抖动性能降低。

虽然PECL以及LVDS也属于方波形式,但这是一种差分输出,主要出现在差分晶振输出逻辑。