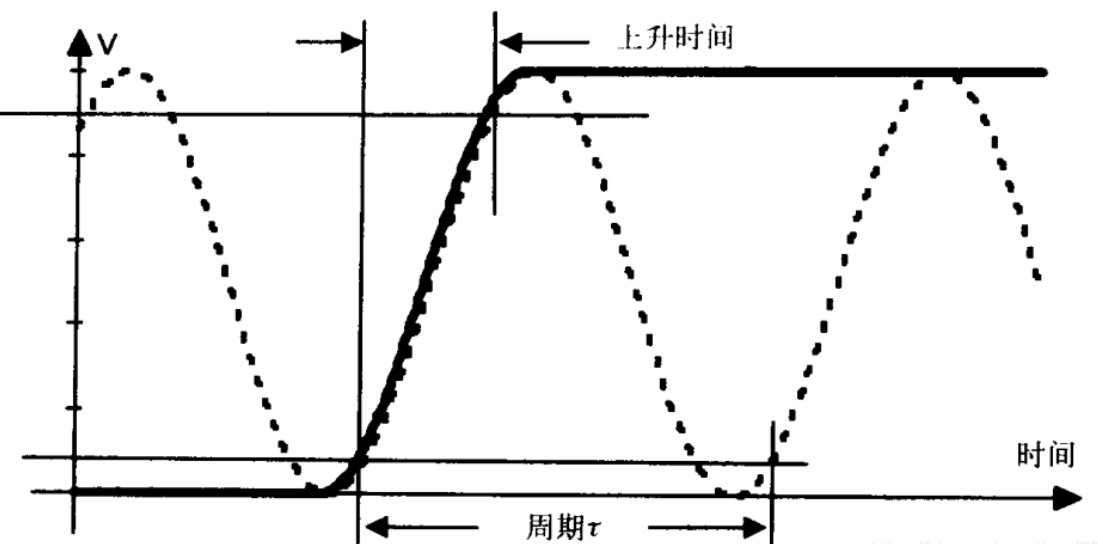

在高速数字系统设计中,关键问题除了晶振所提供的频率信号(Frequency)以外,另外一个关键因素是上升/下降时间(Rise/Fall Time)。

频率(Frequency)

频率是指电流周期的波形在某个单位时间内重复的次数(通常是1s),单位通常为赫兹(Hz)。如在板级比较常用的SPI协议中,若应用为50MHz晶振,则可以表示它的时钟能在1秒钟重复5000万次,它的信号周期长度为1/f,其中f为频率,所以50MHz SPI的一个时钟周期为五千万分之一秒,即20ns。

上升/下降时间(Rise/Fall Time)

上升时间一般定义为从波形的10%处上升到波形的90%处所需要的时间(也有定义规定从20%处上升到80%处的时间)。下降时间的定义与之相同,即从波形的90%处下降到10%所需要的时间。

正弦波信号的上升时间大约是其周期的1/3。

我们可以用ΔI/Δt和Δu/Δt表示某一段时间内电流和电压的变化,如果Δt是一个特变小的时间间隔时,就可以在数学上用dI/dt和du/dt来表示ΔI/Δt和Δu/Δt。dI/dt和du/dt是微分表达式,表示当时间变化为无限小时,电流和电压变化与时间变化之比。在高速电路中,dt可以等于信号的上升或下降时间,正是这个dI/dt和du/dt引出了信号完整性问题。

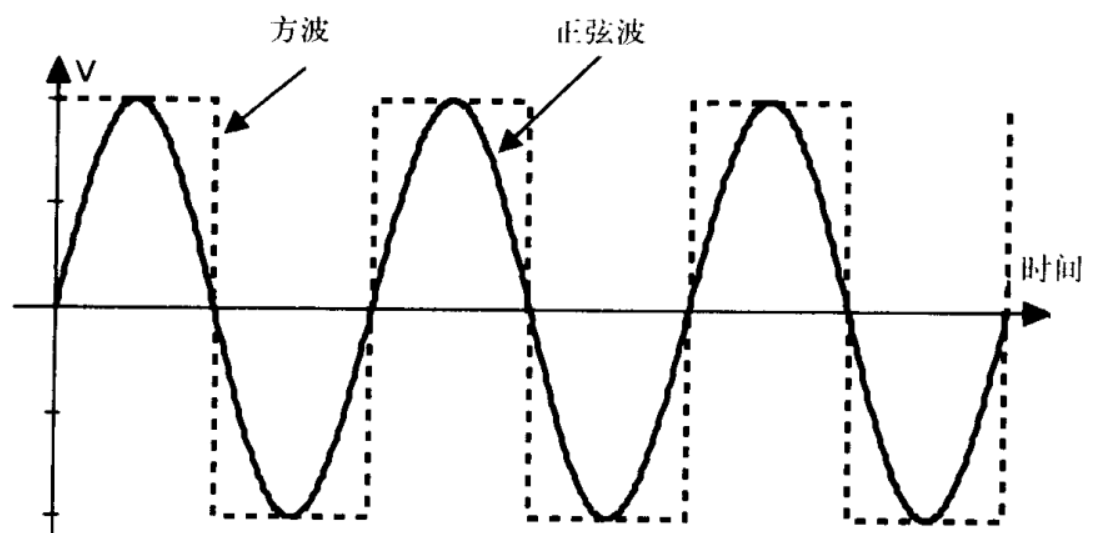

比较

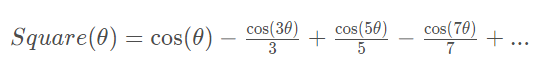

从上图可以看出,虚线的方波和实线的正弦波的频率是相同的,但是方波的上升时间和下降时间要远远小于正弦波的时间。傅里叶定理中指出,方波在自然界中实际是不存在的,但是我们可以利用傅里叶定理变换,用余弦波或正弦波的无穷序列来表示它。理想50%占空比方波是由无穷的奇次谐波组成:

如果在走线的一端输入方波信号,想在另一端也得到方波信号的话,这就意味着电路板不仅能处理数字信号的基频,还必须能处理信号所包含的全部高次谐波分量。所以如果是10MHz的方波,那么我们可能希望能处理15次或者以上的谐波,才能较好的呈现一个方波,那么就意味着我们必须要处理150MHz甚至以上的谐波频率,这就是波形的上升时间和需要重新产生谐波的重要原因。

我们可以使用“带宽”这个词来描述上述要求。带宽指的是能够保持信号完整性的频率范围。可以粗略用下式来确定带宽要求:

带宽(Hz)≈0.3/上升时间

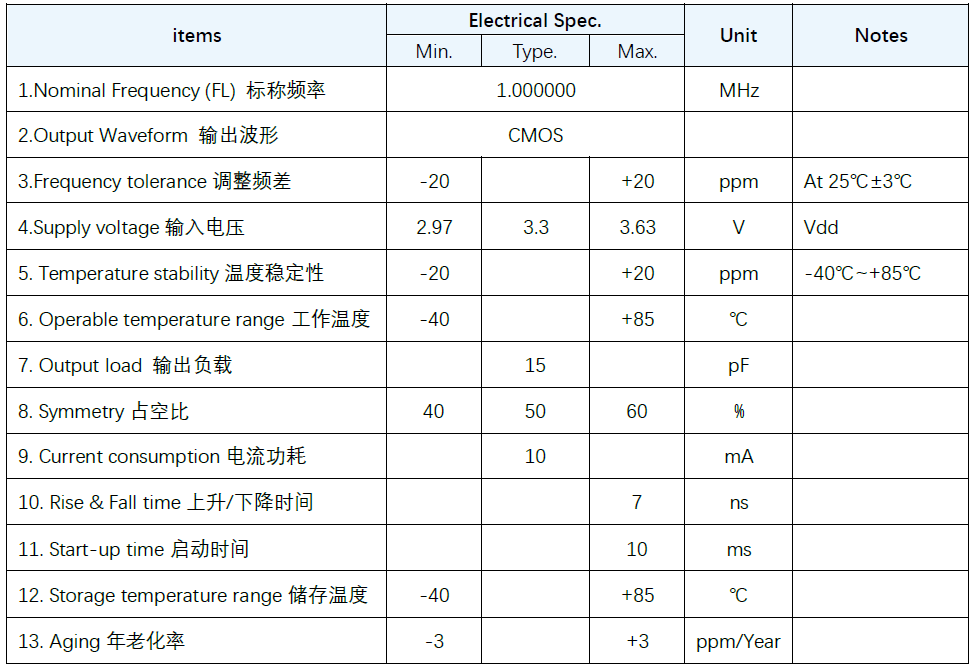

晶诺威科技产1MHz有源晶振OSC7050规格参数如下:

输出类型:方波

#10为上升/下降时间(Rise/Fall Time):7ns

拓展阅读:1ps(皮秒)等于多少(ns)纳秒?

答:1ps等于10^-3ns,即:0.003ns。

晶诺威科技解释如下:

“s”是英文“second”的缩写,中文意思是“秒”。

1ps (皮秒) 1皮秒=0.000,000,000,001秒=10^_12秒。

1ms (毫秒) 1毫秒=0.001秒=10^_3秒 (millisecond)。

1μs (微秒) 1微秒=0.000,001=10^_6秒 (microsecond)。

1ns (纳秒) 1纳秒=0.000,000,001秒=10^_9秒 (nanosecond)。

1fs (飞秒) 1飞秒=0.000,000,000,000,001秒=10^_15秒。

时间单位的换算关系:

一年=12个月,一个月=30天,一天=24小时,1小时=60分钟,1分钟=60秒。

时钟各指针的角度关系:

1、普通钟表相当于圆,其时针或分针走一圈均相当于走过360°角。

2、钟表上的每一个大格对应的角度是:30°。

3、时针每走过1分钟对应的角度应为:0.5°