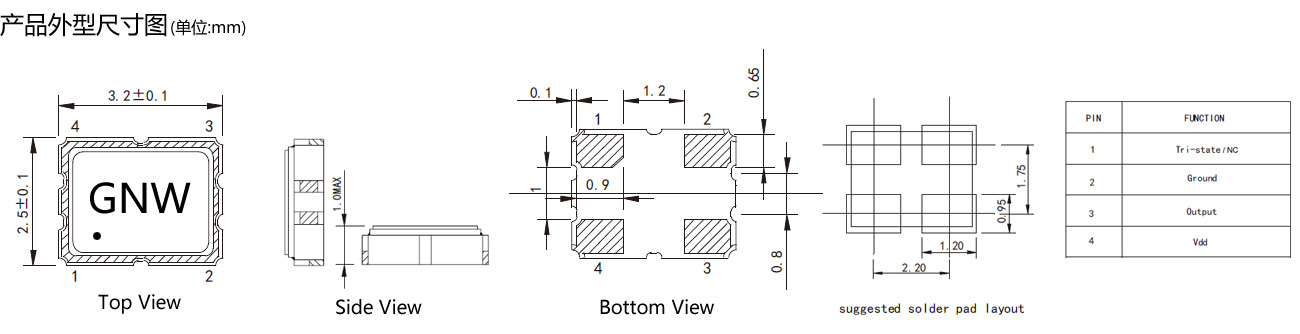

以晶诺威产SMD 3225贴片有源晶振(CMOS输出)为例:

- #1脚为OE功能端,三态功能的开关。

- #2脚GND为接地端。

- #3脚Output为频率输出端。

- #4脚Vdd是工作电压输入端。

在电路设计焊接中,为了稳定运行,建议在Vdd和GND之间连接0.01μF至0.1μF的旁路电容,并尽可能靠近Vdd引脚。

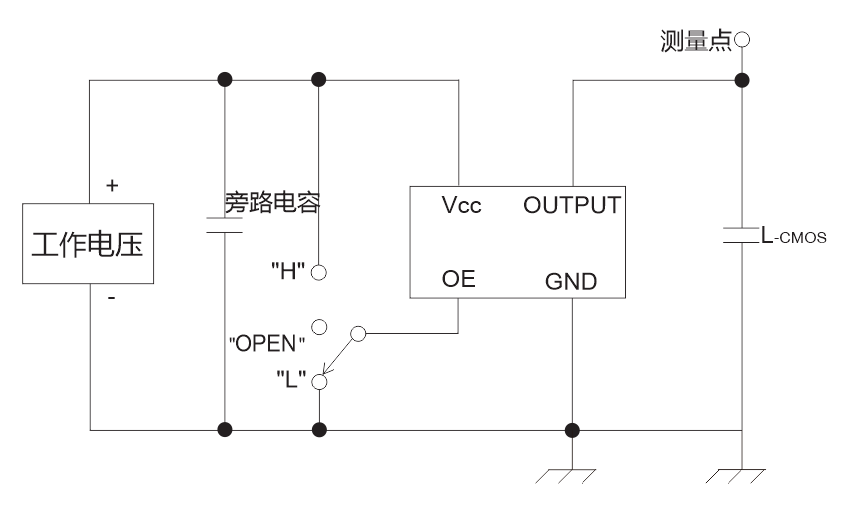

(有源晶振测试电路)

关于有源晶振测试电路测试条件说明如下:

![]() 示波器

示波器

- 带宽应至少比测量频率宽5倍。

- 探头地线应紧贴测试点,引线长度应尽可能短。

- 建议使用微型插座。(不要使用接地线)。

L_CMOS包括探头电容。

L_CMOS包括探头电容。

在靠近器件的Vdd和GND引脚之间应连接一个0.01μF至0.1μF的旁路(bypass)电容。

在靠近器件的Vdd和GND引脚之间应连接一个0.01μF至0.1μF的旁路(bypass)电容。

请使用低阻抗电流表。

请使用低阻抗电流表。

电源Power Supply

电源Power Supply

- 电源启动时间(0 %VCC → 90 %VCC)应超过150 μs。

- 电源阻抗应尽可能的低。