为了减小晶振的频率偏差,晶诺威科技建议可以采取以下措施:

1、 选择高精度、高稳定性的晶振元件。

2、 控制晶振的工作温度和工作电压,使晶振工作条件保持稳定。

3、 采用精确的机械加工和组装工艺,避免机械应力对晶振的影响。

4、 在实际应用中对晶振进行精确的频率校准,提高其准确性。

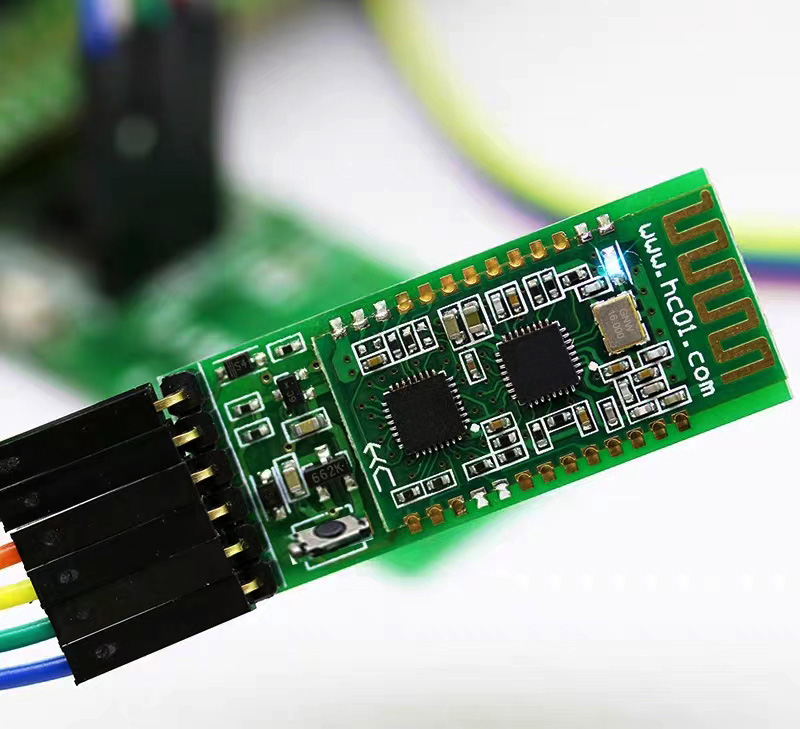

晶振的频率偏差是晶振在实际使用中不可避免的问题,但通过采取一系列的措施,可以减小偏差,提高晶振的精度和稳定性。在电路系统中,高速时钟信号线优先级最高。时钟线是一个敏感信号,频率越高,要求走线尽量简短,以保证信号的失真度达到最小。

因为现在很多电路中,系统晶振时钟频率很高,所以干扰谐波出来的能量也强,谐波除了会从输入与输出两条线导出来外,也会从空间辐射出来,这也导致若PCB中对晶振的布局不够合理,会很容易造成很强的杂散辐射问题,并且一旦产生,很难再通过其他方法来解决,所以在PCB板布局时对晶振和CLK信号线布局非常重要。

由于晶振内部存在石英晶体,受到外部撞击等情况造成晶体断裂,很容易造成晶振不启振,所以通常在电路设计时,要考虑晶振的可靠安装,其位置尽量不要靠近板边、设备外壳等地方。