-

; ) 晶振型号14.7456MHz后的负载电容CL=16pF 是什么意思?

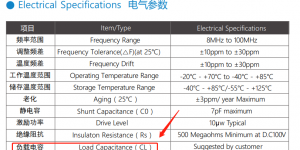

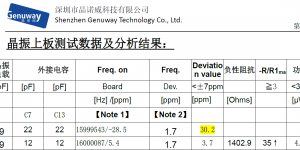

晶振型号14.7456MHz后的负载电容CL=16pF 是什么意思? 答:CL=16pF说明该晶振属于无源晶体谐振器,其负载电容CL(本身电气参数)为16pF。 即使是同一频点的无源晶振,因为对应的芯片方案不同,负载电容CL也不一样。选在晶振的负载电容时。最好参照芯片方案或晶振生产厂家所给的建议,保…时间:2023/06/20

晶振型号14.7456MHz后的负载电容CL=16pF 是什么意思?

晶振型号14.7456MHz后的负载电容CL=16pF 是什么意思? 答:CL=16pF说明该晶振属于无源晶体谐振器,其负载电容CL(本身电气参数)为16pF。 即使是同一频点的无源晶振,因为对应的芯片方案不同,负载电容CL也不一样。选在晶振的负载电容时。最好参照芯片方案或晶振生产厂家所给的建议,保…时间:2023/06/20 -

; ) 无源晶振外接电容与负载电容CL不匹配会出现什么情况?

无源晶振外接电容与负载电容CL不匹配会出现什么情况? 答:如果外接电容过小,晶振输出频率会偏快;反之,如果外接电容过大,晶振输出频率会偏慢,甚至停振。时间:2023/06/19

无源晶振外接电容与负载电容CL不匹配会出现什么情况?

无源晶振外接电容与负载电容CL不匹配会出现什么情况? 答:如果外接电容过小,晶振输出频率会偏快;反之,如果外接电容过大,晶振输出频率会偏慢,甚至停振。时间:2023/06/19 -

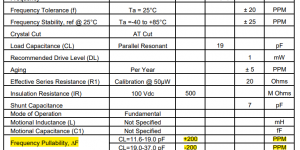

; ) 什么是晶振的频率pullability(拉伸值)?

什么是晶振的频率pullability(拉伸值)? When extra capacitance is added to the oscillator circuit, reducing the oscillator frequency. The level of tuning possible, …时间:2023/06/18

什么是晶振的频率pullability(拉伸值)?

什么是晶振的频率pullability(拉伸值)? When extra capacitance is added to the oscillator circuit, reducing the oscillator frequency. The level of tuning possible, …时间:2023/06/18 -

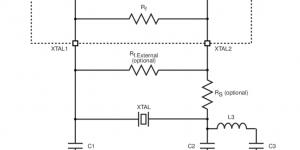

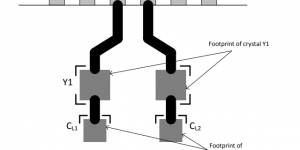

; ) 泛音晶振的泛音振荡电路图

(泛音晶振的泛音电路图) 不同于基频(Fundamental Frequency)晶振,泛音(Overtone Frequency)晶振需要在泛音振荡电路中才能输出所需频率。 拓展阅读: 晶振输出频率是目标频率三分之一的解决方案 晶振输出频率是目标频率三倍的解决方案时间:2023/06/17

泛音晶振的泛音振荡电路图

(泛音晶振的泛音电路图) 不同于基频(Fundamental Frequency)晶振,泛音(Overtone Frequency)晶振需要在泛音振荡电路中才能输出所需频率。 拓展阅读: 晶振输出频率是目标频率三分之一的解决方案 晶振输出频率是目标频率三倍的解决方案时间:2023/06/17 -

; ) 等效串联电阻Rs (ESR: Equivalent Series Resistance) 与负阻Negative Resistance

关于无源晶振(晶体谐振器)起振电路中的等效串联电阻Rs (ESR: Equivalent Series Resistance) 与负阻Negative Resistance,晶诺威科技解释如下: Rs or equivalent series resistance (ESR) is a parame…时间:2023/06/16

等效串联电阻Rs (ESR: Equivalent Series Resistance) 与负阻Negative Resistance

关于无源晶振(晶体谐振器)起振电路中的等效串联电阻Rs (ESR: Equivalent Series Resistance) 与负阻Negative Resistance,晶诺威科技解释如下: Rs or equivalent series resistance (ESR) is a parame…时间:2023/06/16 -

; ) 24MHz无源晶振EMC辐射超标问题分析与建议

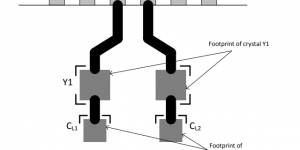

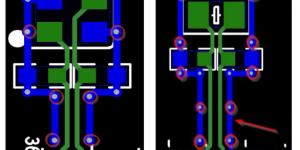

(4引线无源晶振与2引线无源晶振包地图示) 晶诺威科技关于24MHz无源晶振EMC辐射超标问题,分析与建议如下: 问题描述 某款触屏控制电路板,由于其外置无源贴片晶振SMD3225-4P 24MHz晶振布线不合理,导致EMC辐射超标。 原因分析 EMC三要素是干扰源,被干扰对象和干扰路径。而晶振作为…时间:2023/06/15

24MHz无源晶振EMC辐射超标问题分析与建议

(4引线无源晶振与2引线无源晶振包地图示) 晶诺威科技关于24MHz无源晶振EMC辐射超标问题,分析与建议如下: 问题描述 某款触屏控制电路板,由于其外置无源贴片晶振SMD3225-4P 24MHz晶振布线不合理,导致EMC辐射超标。 原因分析 EMC三要素是干扰源,被干扰对象和干扰路径。而晶振作为…时间:2023/06/15 -

; ) 常见晶振故障现象及对应策略

晶振故障现象可能包括设备无法正常启动、频率不稳定、输出信号幅度衰减等。晶诺威科技归纳对应策略如下: 测量晶振频率 电路板上电,使用频率计或示波器测量晶振的输出频率。确认晶振输出频率是否与规定值一致,以及是否存在频率漂移现象。如果发现频率异常,可能是晶振故障或外部环境因素影响。 检查晶振周围元件 检查…时间:2023/06/14

常见晶振故障现象及对应策略

晶振故障现象可能包括设备无法正常启动、频率不稳定、输出信号幅度衰减等。晶诺威科技归纳对应策略如下: 测量晶振频率 电路板上电,使用频率计或示波器测量晶振的输出频率。确认晶振输出频率是否与规定值一致,以及是否存在频率漂移现象。如果发现频率异常,可能是晶振故障或外部环境因素影响。 检查晶振周围元件 检查…时间:2023/06/14 -

; ) 电容太大会导致8MHz晶振不起振且无波形输出吗?

电容太大会导致8MHz晶振不起振且无波形输出吗? 答: 会!如果8MHz无源晶振外接的匹配电容太大,会发生起振困难或不起振现象。晶振在停振情况下自然也不会有波形输出。 拓展阅读: 关于晶振波形 一般无源晶振是正弦波,有源晶振是方波。 正弦波与方波对比如下: 正弦波英文:Sine Wave 正弦波输出…时间:2023/06/14

电容太大会导致8MHz晶振不起振且无波形输出吗?

电容太大会导致8MHz晶振不起振且无波形输出吗? 答: 会!如果8MHz无源晶振外接的匹配电容太大,会发生起振困难或不起振现象。晶振在停振情况下自然也不会有波形输出。 拓展阅读: 关于晶振波形 一般无源晶振是正弦波,有源晶振是方波。 正弦波与方波对比如下: 正弦波英文:Sine Wave 正弦波输出…时间:2023/06/14 -

; ) SMD3225无源贴片晶振12PF和20PF有什么区别?

SMD3225无源贴片晶振12PF和20PF有什么区别? 答:针对无源晶振(晶体谐振器/Crystal/Resonator)而言,其负载电容CL不同,会导致外接电容大小也不一样。在外接电容匹配错误的情况下,无源晶振容易发生频率偏差过大或起振慢等问题。 从应用方案来看,晶振的负载电容CL是由其关联芯片…时间:2023/06/14

SMD3225无源贴片晶振12PF和20PF有什么区别?

SMD3225无源贴片晶振12PF和20PF有什么区别? 答:针对无源晶振(晶体谐振器/Crystal/Resonator)而言,其负载电容CL不同,会导致外接电容大小也不一样。在外接电容匹配错误的情况下,无源晶振容易发生频率偏差过大或起振慢等问题。 从应用方案来看,晶振的负载电容CL是由其关联芯片…时间:2023/06/14 -

; ) 关于晶振频率偏差对RF射频类产品的影响

关于晶振频率偏差对RF射频类产品的影响,晶诺威科技解释如下: The total tolerance of a crystal is dependent on three factors: 晶体谐振器的总频率偏差基于三个因素: Production tolerance 生产时造成的频率偏差 Temp…时间:2023/06/13

关于晶振频率偏差对RF射频类产品的影响

关于晶振频率偏差对RF射频类产品的影响,晶诺威科技解释如下: The total tolerance of a crystal is dependent on three factors: 晶体谐振器的总频率偏差基于三个因素: Production tolerance 生产时造成的频率偏差 Temp…时间:2023/06/13