-

; ) 微型晶振:让智能行动装置与运动健身无缝衔接

(微型晶振:让智能行动装置与健身运动无缝衔接) 生命在于运动!智能行动装置在功能上的优化离不开微型晶振的功劳。智能行动装置(数据处理、分析及无线传输等)功能,列举如下: 通话 导航 计步 骑行 爬山 游泳 体温 呼吸频率 心率及ECG 心电分析 血管健康监测 …时间:2022/09/14

微型晶振:让智能行动装置与运动健身无缝衔接

(微型晶振:让智能行动装置与健身运动无缝衔接) 生命在于运动!智能行动装置在功能上的优化离不开微型晶振的功劳。智能行动装置(数据处理、分析及无线传输等)功能,列举如下: 通话 导航 计步 骑行 爬山 游泳 体温 呼吸频率 心率及ECG 心电分析 血管健康监测 …时间:2022/09/14 -

; ) 电子手表每月误差在±30秒正常吗?

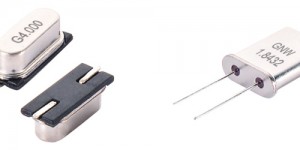

电子手表每月误差在±30秒正常吗? 首先,由于电子手表在走时方面的确存在误差现象,那么每月误差±30秒算是正常范围吗? 电子手表里面的核心电子元件是频率为32.768KHz的石英晶振,常见为圆柱体无源晶振与贴片式无源晶振两种类型。在无源晶振的应用中,我们需要特别注意晶振的精度选择和晶振负载电容的匹配…时间:2022/09/13

电子手表每月误差在±30秒正常吗?

电子手表每月误差在±30秒正常吗? 首先,由于电子手表在走时方面的确存在误差现象,那么每月误差±30秒算是正常范围吗? 电子手表里面的核心电子元件是频率为32.768KHz的石英晶振,常见为圆柱体无源晶振与贴片式无源晶振两种类型。在无源晶振的应用中,我们需要特别注意晶振的精度选择和晶振负载电容的匹配…时间:2022/09/13 -

; ) 4脚/焊盘SMD3225晶体/无源晶振如何接线?

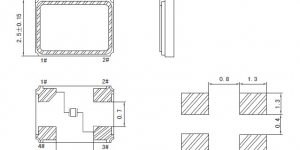

(晶诺威科技产SMD3225无源晶体谐振器尺寸及引脚说明) 4脚/焊盘SMD3225晶体/无源晶振如何接线? 如上图所示,4脚/焊盘SMD3225晶体/无源晶振的功能脚(频率输入脚与频率输出脚)为#1和#3,这两个脚不分方向,焊反没关系。 #2和#4与晶振金属外壳连接,可悬空,也可接地。针对RF射频…时间:2022/09/12

4脚/焊盘SMD3225晶体/无源晶振如何接线?

(晶诺威科技产SMD3225无源晶体谐振器尺寸及引脚说明) 4脚/焊盘SMD3225晶体/无源晶振如何接线? 如上图所示,4脚/焊盘SMD3225晶体/无源晶振的功能脚(频率输入脚与频率输出脚)为#1和#3,这两个脚不分方向,焊反没关系。 #2和#4与晶振金属外壳连接,可悬空,也可接地。针对RF射频…时间:2022/09/12 -

; ) FC-135/SMD3215晶振32.768KHz输入与输出一样吗?

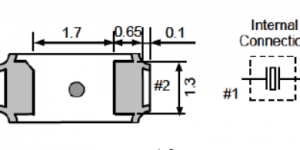

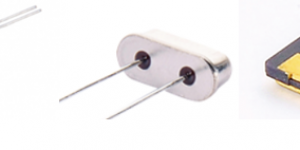

FC-135/SMD3215晶振32.768KHz输入与输出一样吗? 答:如上图所示,对该晶振本身而言,信号输入端和信号输出端是一样的。 解释: FC-135/SMD3215晶振32.768KHz属于两脚无源贴片晶振,即石英晶体谐振器。#1和#2在电路应用中不做方向性区分。 解释: 无源晶振是一种无…时间:2022/09/05

FC-135/SMD3215晶振32.768KHz输入与输出一样吗?

FC-135/SMD3215晶振32.768KHz输入与输出一样吗? 答:如上图所示,对该晶振本身而言,信号输入端和信号输出端是一样的。 解释: FC-135/SMD3215晶振32.768KHz属于两脚无源贴片晶振,即石英晶体谐振器。#1和#2在电路应用中不做方向性区分。 解释: 无源晶振是一种无…时间:2022/09/05 -

; ) 超出指定工作温度晶振OSC7050 50MHz 会工作吗?

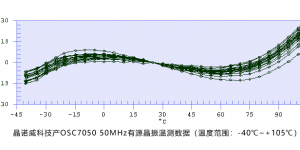

超出指定工作温度晶振OSC7050 50MHz 会工作吗? 答:一般情况下,若超出晶振规格书指定的工作温度区间,晶振会工作,但可能会出现以下故障: 起振困难 频率精度超差 加速老化 举例如下: 如果某型号晶振指定温度范围为-20℃~70℃,而实际应用在-40℃~+85℃之内时,晶振或许不会停振,但其…时间:2022/09/01

超出指定工作温度晶振OSC7050 50MHz 会工作吗?

超出指定工作温度晶振OSC7050 50MHz 会工作吗? 答:一般情况下,若超出晶振规格书指定的工作温度区间,晶振会工作,但可能会出现以下故障: 起振困难 频率精度超差 加速老化 举例如下: 如果某型号晶振指定温度范围为-20℃~70℃,而实际应用在-40℃~+85℃之内时,晶振或许不会停振,但其…时间:2022/09/01 -

; ) 晶振突然坏了怎么办?

晶振分无源晶振和有源晶振两大类,是数字电路中的重要部件,其作用是向显卡、网卡、主板、蓝牙模组、WiFi模组、RF模组等提供基准时钟信号,一旦工作频率不稳定就会造成相关设备功能不稳定。 晶振本身原因: SPDB不良、DLD不良、阻抗过大、频率精度超差、频率牵引力不足或过大等(主要针对RF射频类产品)。…时间:2022/08/26

晶振突然坏了怎么办?

晶振分无源晶振和有源晶振两大类,是数字电路中的重要部件,其作用是向显卡、网卡、主板、蓝牙模组、WiFi模组、RF模组等提供基准时钟信号,一旦工作频率不稳定就会造成相关设备功能不稳定。 晶振本身原因: SPDB不良、DLD不良、阻抗过大、频率精度超差、频率牵引力不足或过大等(主要针对RF射频类产品)。…时间:2022/08/26 -

; ) 晶振焊反了怎么办?

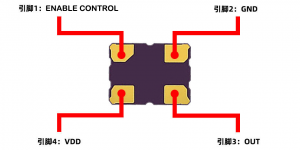

晶振焊反了怎么办? 晶诺威科技解释如下: 二脚、三脚晶振为无源晶振,焊反没关系。也就是说,无源晶振的频率输入脚与频率输出脚不必加以区分,而三脚晶振中间脚为接地脚,接GND即可。 关于晶诺威科技产四脚晶振的特别说明 若为无源晶振,焊反没关系;即:频率管脚1和频率管脚3为无极性引脚,接反没关系;脚2与脚…时间:2022/08/23

晶振焊反了怎么办?

晶振焊反了怎么办? 晶诺威科技解释如下: 二脚、三脚晶振为无源晶振,焊反没关系。也就是说,无源晶振的频率输入脚与频率输出脚不必加以区分,而三脚晶振中间脚为接地脚,接GND即可。 关于晶诺威科技产四脚晶振的特别说明 若为无源晶振,焊反没关系;即:频率管脚1和频率管脚3为无极性引脚,接反没关系;脚2与脚…时间:2022/08/23 -

; ) 跌落、物理冲击及超声波对晶振的影响

针对跌落、物理冲击及超声波对晶振的影响,解释如下: 跌落 从设计角度而言,即使石英晶振从高度75cm处落到硬质木板上3次,按照设计不会发生什么问题。但因落下时的不同条件而异,有可能导致石英晶片破损。 物理冲击 石英晶振与电阻及电容等电子元件不同,由于在内部对石英晶片进行了密封保护,因此关于在自动安装…时间:2022/08/17

跌落、物理冲击及超声波对晶振的影响

针对跌落、物理冲击及超声波对晶振的影响,解释如下: 跌落 从设计角度而言,即使石英晶振从高度75cm处落到硬质木板上3次,按照设计不会发生什么问题。但因落下时的不同条件而异,有可能导致石英晶片破损。 物理冲击 石英晶振与电阻及电容等电子元件不同,由于在内部对石英晶片进行了密封保护,因此关于在自动安装…时间:2022/08/17 -

; ) 关于晶振应用的一些具体说明

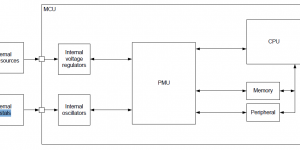

建议首先进行硬件验证,步骤如下: 1. 确保芯片焊接OK,排除焊反或虚焊问题。 2. 确保地和电源无短路,避免连接稳压电压进行下一步测试时烧毁电路板。 3. 接通稳压电源,查看并确保各个电压输出OK。 4. 确保晶振引脚焊接正确,避免短路或虚焊。有些 芯片 上电后晶振就会起振,可用示波器或频率计测试…时间:2022/08/16

关于晶振应用的一些具体说明

建议首先进行硬件验证,步骤如下: 1. 确保芯片焊接OK,排除焊反或虚焊问题。 2. 确保地和电源无短路,避免连接稳压电压进行下一步测试时烧毁电路板。 3. 接通稳压电源,查看并确保各个电压输出OK。 4. 确保晶振引脚焊接正确,避免短路或虚焊。有些 芯片 上电后晶振就会起振,可用示波器或频率计测试…时间:2022/08/16 -

; ) 电容在数字电路中都有哪些作用?

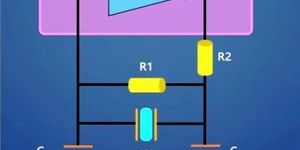

关于电容的作用,归纳九点如下: 1、 隔直流 阻止直流通过而让交流通过。 2、 旁路(去耦) 为交流电路中某些并联的元件提供低阻抗通路。 3、 耦合 作为两个电路之间的连接,允许交流信号通过并传输到下一级电路。 4、 滤波 这个对电路而言很重要,CPU背后的电容基本都是这个作用。 5、 温度补偿 针…时间:2022/08/10

电容在数字电路中都有哪些作用?

关于电容的作用,归纳九点如下: 1、 隔直流 阻止直流通过而让交流通过。 2、 旁路(去耦) 为交流电路中某些并联的元件提供低阻抗通路。 3、 耦合 作为两个电路之间的连接,允许交流信号通过并传输到下一级电路。 4、 滤波 这个对电路而言很重要,CPU背后的电容基本都是这个作用。 5、 温度补偿 针…时间:2022/08/10