-

; ) 如何识别晶振的频率?

晶振的主要参数有标称频率(Nominal Frequency)、老化率(Aging)、调整频差(Frequency Tolerance)、频率稳定度(Frequency Stability)、温度范围(Operating Temperature)、等效阻抗(Equivalent Series Res…时间:2022/08/08

如何识别晶振的频率?

晶振的主要参数有标称频率(Nominal Frequency)、老化率(Aging)、调整频差(Frequency Tolerance)、频率稳定度(Frequency Stability)、温度范围(Operating Temperature)、等效阻抗(Equivalent Series Res…时间:2022/08/08 -

; ) 无源晶振,有源晶振与石英晶体的关系

石英晶体谐振器、石英晶体振荡器、石英晶体滤波器均为石英晶体元器件。我们常说的无源晶振其全称是石英晶体谐振器,而有源晶振则是指石英晶体振荡器,它们都是石英晶体元器件中的一种。 石英晶体是一种压电晶体。压电晶体当受特定方向挤压或拉伸时,它的两端就会产生不同的电荷。根据效应情况不同,分为正压电效应与逆压电…时间:2022/08/07

无源晶振,有源晶振与石英晶体的关系

石英晶体谐振器、石英晶体振荡器、石英晶体滤波器均为石英晶体元器件。我们常说的无源晶振其全称是石英晶体谐振器,而有源晶振则是指石英晶体振荡器,它们都是石英晶体元器件中的一种。 石英晶体是一种压电晶体。压电晶体当受特定方向挤压或拉伸时,它的两端就会产生不同的电荷。根据效应情况不同,分为正压电效应与逆压电…时间:2022/08/07 -

; ) 共享单车都用到哪些晶振?

在我们生活中,共享单车里使用的晶振通常有两颗:一颗无源贴片晶振和一颗高精度TCXO温补晶振。 这颗无源晶振应用于共享单车的移动电源里面,常见标称频率为16MHz、12MHz和32MHz,封装方式为SMD贴片式,尺寸为3.2mm*2.5mm或2.5mm*2.0mm。 高精度TCXO温补晶振的作用是精准…时间:2022/08/06

共享单车都用到哪些晶振?

在我们生活中,共享单车里使用的晶振通常有两颗:一颗无源贴片晶振和一颗高精度TCXO温补晶振。 这颗无源晶振应用于共享单车的移动电源里面,常见标称频率为16MHz、12MHz和32MHz,封装方式为SMD贴片式,尺寸为3.2mm*2.5mm或2.5mm*2.0mm。 高精度TCXO温补晶振的作用是精准…时间:2022/08/06 -

; ) 晶诺威科技49SMD封装晶振4MHz可靠度测试数据

(49SMD晶振4MHz产品图片) 晶诺威科技49SMD封装晶振4MHz可靠度测试数据,整理如下: 测试项目:自由跌落 测试设备:跌落台,30mm厚硬木板,250B 测试条件:从75cm高自由跌落至30mm厚硬木板上,跌落3次。 测试数据如下: 测试项目:低频振动 测试设备:振动测试台…时间:2022/08/04

晶诺威科技49SMD封装晶振4MHz可靠度测试数据

(49SMD晶振4MHz产品图片) 晶诺威科技49SMD封装晶振4MHz可靠度测试数据,整理如下: 测试项目:自由跌落 测试设备:跌落台,30mm厚硬木板,250B 测试条件:从75cm高自由跌落至30mm厚硬木板上,跌落3次。 测试数据如下: 测试项目:低频振动 测试设备:振动测试台…时间:2022/08/04 -

; ) 关于外接晶振符号XTAL/CLKIN说明

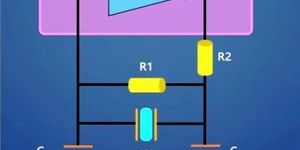

XTAL表示外部晶振(或外接晶振)(External Crystal Oscillator)。而外部晶振常常连接至单片机的引脚,常常使用XTAL加上数字表示连接外部晶振。 XTAL1 接外部晶振和微调电容的一端,在片内它是振荡器反相放大器和时钟发生器的输入端;若使用外部时钟时,该引脚接地或悬空。 X…时间:2022/08/04

关于外接晶振符号XTAL/CLKIN说明

XTAL表示外部晶振(或外接晶振)(External Crystal Oscillator)。而外部晶振常常连接至单片机的引脚,常常使用XTAL加上数字表示连接外部晶振。 XTAL1 接外部晶振和微调电容的一端,在片内它是振荡器反相放大器和时钟发生器的输入端;若使用外部时钟时,该引脚接地或悬空。 X…时间:2022/08/04 -

; ) 一些数字电路为何要用有源晶振要代替无源晶振?

目前,为了避免繁琐的电路匹配,越来越多的数字电路改为有源晶振应用方案。有源晶振有内置电路,所以不存在电路匹配问题,极大避免了晶振不起振问题的发生。另外,有源晶振时钟电路凸显其稳定性优势。 晶振正常工作无法离开IC。因为无源晶振本身输出能力有限,只能输出以毫瓦为单位的电能量。在 IC(集成电路) 内部…时间:2022/08/04

一些数字电路为何要用有源晶振要代替无源晶振?

目前,为了避免繁琐的电路匹配,越来越多的数字电路改为有源晶振应用方案。有源晶振有内置电路,所以不存在电路匹配问题,极大避免了晶振不起振问题的发生。另外,有源晶振时钟电路凸显其稳定性优势。 晶振正常工作无法离开IC。因为无源晶振本身输出能力有限,只能输出以毫瓦为单位的电能量。在 IC(集成电路) 内部…时间:2022/08/04 -

; ) 无源晶振起振三要素

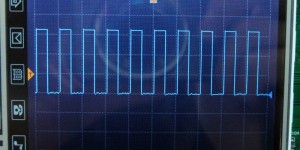

作为数字电路中最常见频率器件,无源晶振属于被动频控元件。 无源晶振电路工作原理 无源晶振电路的工作原理是利用晶体的压电效应和共振效应。当外加电压作用于晶体时,晶体会产生机械振动,这种振动会产生电荷,从而形成一个稳定的振荡信号。这个振荡信号经过放大就成为了单片机的时钟信号。 无源晶振起振条件 在IC(…时间:2022/08/03

无源晶振起振三要素

作为数字电路中最常见频率器件,无源晶振属于被动频控元件。 无源晶振电路工作原理 无源晶振电路的工作原理是利用晶体的压电效应和共振效应。当外加电压作用于晶体时,晶体会产生机械振动,这种振动会产生电荷,从而形成一个稳定的振荡信号。这个振荡信号经过放大就成为了单片机的时钟信号。 无源晶振起振条件 在IC(…时间:2022/08/03 -

; ) 振荡器、石英晶振和晶体振荡器是什么关系?

振荡器、石英晶振和晶体振荡器是什么关系?解析如下: 振荡器 振荡器是用来产生重复电子讯号(通常是正弦波或方波)的电子元件,其构成的电路叫做振荡器。换句话说,振荡器是能将直流电转换为具有一定频率交流电信号输出的电子电路或装置。振荡器分为两种,一种是使用内部时钟的振荡器,另外一种是使用外部时钟的振荡器,…时间:2022/08/02

振荡器、石英晶振和晶体振荡器是什么关系?

振荡器、石英晶振和晶体振荡器是什么关系?解析如下: 振荡器 振荡器是用来产生重复电子讯号(通常是正弦波或方波)的电子元件,其构成的电路叫做振荡器。换句话说,振荡器是能将直流电转换为具有一定频率交流电信号输出的电子电路或装置。振荡器分为两种,一种是使用内部时钟的振荡器,另外一种是使用外部时钟的振荡器,…时间:2022/08/02 -

; ) 频率信号发生器和石英晶振的关系

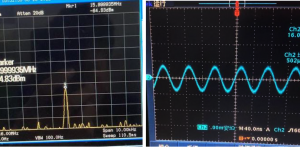

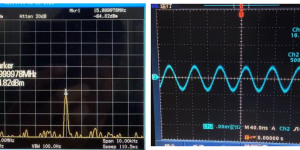

通信系统的频率发生器(时钟发生器)中的晶振是石英晶振,我们利用石英晶体的压电效应制成谐振组件。石英谐振器能形成一个振荡脉冲,在系统工作的时候为数据处理设备提供一个高精度及高稳定频率的时钟信号。 石英晶振的出现直接取代了LC 选频电路,被广泛应用于各类电子产品中。作为电感组件的石英谐振器在振荡电路可以…时间:2022/08/02

频率信号发生器和石英晶振的关系

通信系统的频率发生器(时钟发生器)中的晶振是石英晶振,我们利用石英晶体的压电效应制成谐振组件。石英谐振器能形成一个振荡脉冲,在系统工作的时候为数据处理设备提供一个高精度及高稳定频率的时钟信号。 石英晶振的出现直接取代了LC 选频电路,被广泛应用于各类电子产品中。作为电感组件的石英谐振器在振荡电路可以…时间:2022/08/02 -

; ) 晶体谐振器/无源晶振工作电流及激励功率

激励功率(激励电平)的大小直接影响石英谐振器(晶体/晶体谐振器)的性能,一般电流取值在范围在70μA~100μA为佳;用激励功率表示时,一般取值范围在10μW~100μW为最佳。 电路设计时,一定要严格控制石英谐振器在规定的激励功率下工作,以便充分发挥石英谐振器的正常性能。激励电流测试位置如下: 拓…时间:2022/08/01

晶体谐振器/无源晶振工作电流及激励功率

激励功率(激励电平)的大小直接影响石英谐振器(晶体/晶体谐振器)的性能,一般电流取值在范围在70μA~100μA为佳;用激励功率表示时,一般取值范围在10μW~100μW为最佳。 电路设计时,一定要严格控制石英谐振器在规定的激励功率下工作,以便充分发挥石英谐振器的正常性能。激励电流测试位置如下: 拓…时间:2022/08/01