-

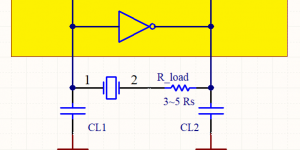

; ) 晶振电路:Pierce电路的负性阻抗-R计算公式

关于负性阻抗的概念,我们知道阻性元件都需要消耗功率,那么负性阻抗就是提供功率的器件,那就相当于激励源。 负性阻抗过小将导致晶振电路不起振,因此可以通过计算或测量负阻来防止驱动功率不足的问题。负性阻抗并不是石英晶体的产品参数,而是振荡电路的一项重要特性参数。振荡电路的负阻越大,振荡电路越容易起振。 注…时间:2021/11/13

晶振电路:Pierce电路的负性阻抗-R计算公式

关于负性阻抗的概念,我们知道阻性元件都需要消耗功率,那么负性阻抗就是提供功率的器件,那就相当于激励源。 负性阻抗过小将导致晶振电路不起振,因此可以通过计算或测量负阻来防止驱动功率不足的问题。负性阻抗并不是石英晶体的产品参数,而是振荡电路的一项重要特性参数。振荡电路的负阻越大,振荡电路越容易起振。 注…时间:2021/11/13 -

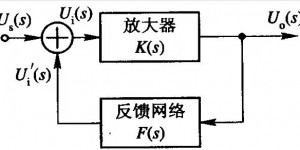

; ) 反馈型振荡器电路与时钟产生器

关于反馈型振荡器电路与时钟产生器工作原理介绍如下: 反馈型振荡器 指是由放大器和反馈网络组成的一个闭合环路。 反馈型振荡器由放大器和反馈网络两大部分组成。放大器通常以某种选频网络(如振荡回路)作负载, 是一种调谐放大器。反馈网络一般是由无源器件组成的线性网络。 反馈型振荡器工作原理 起振------…时间:2021/11/13

反馈型振荡器电路与时钟产生器

关于反馈型振荡器电路与时钟产生器工作原理介绍如下: 反馈型振荡器 指是由放大器和反馈网络组成的一个闭合环路。 反馈型振荡器由放大器和反馈网络两大部分组成。放大器通常以某种选频网络(如振荡回路)作负载, 是一种调谐放大器。反馈网络一般是由无源器件组成的线性网络。 反馈型振荡器工作原理 起振------…时间:2021/11/13 -

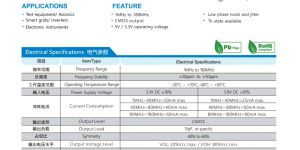

; ) 直插有源晶振/晶体振荡器PXO DIP14规格参数介绍

(直插有源晶振/晶体振荡器PXO DIP14) 直插有源晶振/晶体振荡器PXO DIP14主要电气参数 频率范围:1.000 Mhz to 100.000 Mhz 体积:20.4x12.8x5.3mm 工作电压:3.3V or 5V 调整频差:±10ppm to ±30ppm 工作温度(°C):-2…时间:2021/11/12

直插有源晶振/晶体振荡器PXO DIP14规格参数介绍

(直插有源晶振/晶体振荡器PXO DIP14) 直插有源晶振/晶体振荡器PXO DIP14主要电气参数 频率范围:1.000 Mhz to 100.000 Mhz 体积:20.4x12.8x5.3mm 工作电压:3.3V or 5V 调整频差:±10ppm to ±30ppm 工作温度(°C):-2…时间:2021/11/12 -

; ) 直插有源晶振/晶体振荡器PXO DIP8规格参数介绍

直插有源晶振/晶体振荡器PXO DIP8主要电气参数 频率范围:1.000 MHz to 180.000 MHz 体积:12.9x12.9x5.3mm 工作电压:3.3V or 5V 总频差:±20ppm to ±50ppm 工作温度(°C):-20~+70,-40~+85 输出方式:10 TTL …时间:2021/11/12

直插有源晶振/晶体振荡器PXO DIP8规格参数介绍

直插有源晶振/晶体振荡器PXO DIP8主要电气参数 频率范围:1.000 MHz to 180.000 MHz 体积:12.9x12.9x5.3mm 工作电压:3.3V or 5V 总频差:±20ppm to ±50ppm 工作温度(°C):-20~+70,-40~+85 输出方式:10 TTL …时间:2021/11/12 -

; ) IC不良导致晶振不起振问题

判定IC不良导致晶振不起振的最直接的方法就是做交换实验,建议如下: 首先,取下怀疑“不起振晶振”,换到OK电路板,上电测试IC是否正常捕捉到晶振正常频率信号。若IC已正常工作,说明晶振OK。进一步,把OK电路板晶振取下,焊接到NG电路板上电测试,若IC不工作,则可以反证IC不良。 补充说明,若尝试给…时间:2021/11/12

IC不良导致晶振不起振问题

判定IC不良导致晶振不起振的最直接的方法就是做交换实验,建议如下: 首先,取下怀疑“不起振晶振”,换到OK电路板,上电测试IC是否正常捕捉到晶振正常频率信号。若IC已正常工作,说明晶振OK。进一步,把OK电路板晶振取下,焊接到NG电路板上电测试,若IC不工作,则可以反证IC不良。 补充说明,若尝试给…时间:2021/11/12 -

; ) 晶振的重要参数有哪些?

晶振的重要参数有哪些? 1、针对32.768KHz晶振,其重要参数是频率精度、负载电容及晶振规格尺寸。如果是贴片晶振,需要通过晶振规格书查看晶振具体体积、并进一步了解晶振的负载和频率精度。插件晶振也如此,常见32.768KHz插件晶振为两脚圆柱型(2*6及3*8),两引脚为无极性引脚,不具备方向性。…时间:2021/11/11

晶振的重要参数有哪些?

晶振的重要参数有哪些? 1、针对32.768KHz晶振,其重要参数是频率精度、负载电容及晶振规格尺寸。如果是贴片晶振,需要通过晶振规格书查看晶振具体体积、并进一步了解晶振的负载和频率精度。插件晶振也如此,常见32.768KHz插件晶振为两脚圆柱型(2*6及3*8),两引脚为无极性引脚,不具备方向性。…时间:2021/11/11 -

; ) 晶振的输出频率精度可以调整吗?

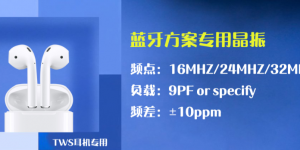

±10ppm 24MHz无源晶振输出频率 晶振的输出频率精度可以调吗? 答:无源晶振的输出频率精度可以微调,而有源晶振的输出频率精度不可以调。 有源晶振已内置包含IC及电容电阻在内的最佳匹配电路,输出频率精度已经固定,因此不可调。如果有源晶振频率精度无法满足芯片要求,请选择更高规格的…时间:2021/11/11

晶振的输出频率精度可以调整吗?

±10ppm 24MHz无源晶振输出频率 晶振的输出频率精度可以调吗? 答:无源晶振的输出频率精度可以微调,而有源晶振的输出频率精度不可以调。 有源晶振已内置包含IC及电容电阻在内的最佳匹配电路,输出频率精度已经固定,因此不可调。如果有源晶振频率精度无法满足芯片要求,请选择更高规格的…时间:2021/11/11 -

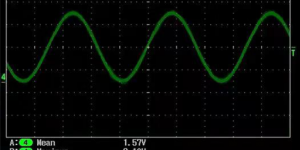

; ) 单片机内部时钟与外部晶振时钟的区别

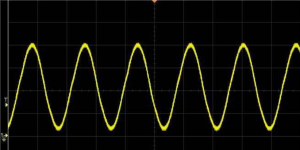

(无源晶振时钟信号:正弦波) 单片机内部时钟 指使用芯片内部振荡电路,精度不高且温飘较大(在温度变化下频率偏差很大,百分之几)。有时为了节省成本、不需要精确定时及计数的情况下可以不用外部时钟。仅使用内部时钟的电子产品常见于低端电子产品,如电子玩具等。 单片机外部晶振时钟 由RC振荡和石英晶振两部分构…时间:2021/11/11

单片机内部时钟与外部晶振时钟的区别

(无源晶振时钟信号:正弦波) 单片机内部时钟 指使用芯片内部振荡电路,精度不高且温飘较大(在温度变化下频率偏差很大,百分之几)。有时为了节省成本、不需要精确定时及计数的情况下可以不用外部时钟。仅使用内部时钟的电子产品常见于低端电子产品,如电子玩具等。 单片机外部晶振时钟 由RC振荡和石英晶振两部分构…时间:2021/11/11 -

; ) 如何判定无源晶振正常起振?

电路板上电后,通过使用示波器观察无源晶振输出波形(正弦波)或频率计数器测量无源晶振实际输出频率是最直接的方式,因为只有晶振振荡电路正常工作,无源晶振的指定功能引脚才会有频率(时钟)信号输出。 单片机的两个信号脚分为晶振频率信号输入脚和晶振频率信号输出脚。一般情况下,举例:若19脚(XTAL1) 是输…时间:2021/11/11

如何判定无源晶振正常起振?

电路板上电后,通过使用示波器观察无源晶振输出波形(正弦波)或频率计数器测量无源晶振实际输出频率是最直接的方式,因为只有晶振振荡电路正常工作,无源晶振的指定功能引脚才会有频率(时钟)信号输出。 单片机的两个信号脚分为晶振频率信号输入脚和晶振频率信号输出脚。一般情况下,举例:若19脚(XTAL1) 是输…时间:2021/11/11 -

; ) 24M晶体频偏20PPM是多少?

PPM是英文Parts Per Million的缩写,表示百万分之几。换句话说:1PPM则代表百万分之一的误差。在这里,PPM值代表晶振的频偏程度,以晶振中心频率为参照点,正确表达方式为±XPPM,+PPM表示的是高于晶振中心频率的程度,-PPM则指的是低于晶振中心频率的程度。 M是英文Millio…时间:2021/11/10

24M晶体频偏20PPM是多少?

PPM是英文Parts Per Million的缩写,表示百万分之几。换句话说:1PPM则代表百万分之一的误差。在这里,PPM值代表晶振的频偏程度,以晶振中心频率为参照点,正确表达方式为±XPPM,+PPM表示的是高于晶振中心频率的程度,-PPM则指的是低于晶振中心频率的程度。 M是英文Millio…时间:2021/11/10