-

; ) 晶振输出频率不稳定是什么原因?

晶振输出频率不稳定是什么原因? 答:晶振输出频率不稳定的原因可能包括内部或外部的干扰、负载变化、温度变化等。可尝试调整电路设计以减少干扰、使用适当的电容匹配、选择合适的温度系数等。时间:2024/03/08

晶振输出频率不稳定是什么原因?

晶振输出频率不稳定是什么原因? 答:晶振输出频率不稳定的原因可能包括内部或外部的干扰、负载变化、温度变化等。可尝试调整电路设计以减少干扰、使用适当的电容匹配、选择合适的温度系数等。时间:2024/03/08 -

; ) LVDS输出148.5MHz差分晶振规格参数介绍

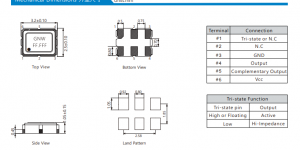

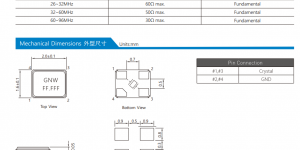

(LVDS输出148.5MHz差分晶振尺寸及引脚功能说明) 晶诺威科技产LVDS输出148.5MHz差分晶振规格参数介绍如下: 主要电气参数: Type(所属类别):Differential Output(差分晶振),Fixed frequency(定频) Output Frequency(输出频率…时间:2024/03/07

LVDS输出148.5MHz差分晶振规格参数介绍

(LVDS输出148.5MHz差分晶振尺寸及引脚功能说明) 晶诺威科技产LVDS输出148.5MHz差分晶振规格参数介绍如下: 主要电气参数: Type(所属类别):Differential Output(差分晶振),Fixed frequency(定频) Output Frequency(输出频率…时间:2024/03/07 -

; ) Half Size(DIP8)/FULL Size(DIP14)Oscillator有源直插晶振40.68MHz

晶诺威科技产Half Size(DIP8) / FULL Size(DIP14) Oscillator有源直插晶振40.68MHz电气参数如下: 所属类型: PXO-DIP08、PXO-DIP14 安装方式:直插式 标称频率:40.68MHz 频率稳定性:±25ppm 工作电压:3.3V、5V 输出…时间:2024/03/07

Half Size(DIP8)/FULL Size(DIP14)Oscillator有源直插晶振40.68MHz

晶诺威科技产Half Size(DIP8) / FULL Size(DIP14) Oscillator有源直插晶振40.68MHz电气参数如下: 所属类型: PXO-DIP08、PXO-DIP14 安装方式:直插式 标称频率:40.68MHz 频率稳定性:±25ppm 工作电压:3.3V、5V 输出…时间:2024/03/07 -

; ) 低电源设计会对振荡器产生什么影响?

低电源设计会对振荡器产生什么影响? 低电源设计对振荡器的影响主要体现在高频振荡器(OSCILLATOR)的设计上。这主要带来两个问题: 在设计高频OSCILLATOR时,可能会面临放大器低的高频增益及高的CRYSTAL等效电阻(ESR)。也就是说,低电源设计可能使得振荡器在高频下的性能受到影响,可能…时间:2024/03/06

低电源设计会对振荡器产生什么影响?

低电源设计会对振荡器产生什么影响? 低电源设计对振荡器的影响主要体现在高频振荡器(OSCILLATOR)的设计上。这主要带来两个问题: 在设计高频OSCILLATOR时,可能会面临放大器低的高频增益及高的CRYSTAL等效电阻(ESR)。也就是说,低电源设计可能使得振荡器在高频下的性能受到影响,可能…时间:2024/03/06 -

; ) 晶振的两种主要振动模式:基频(Fund)与三次泛音(3rd overtone)

关于晶振的两种主要振动模式,晶诺威科技解释如下: 目前,我司产晶振的两种主要振动方式为:基频(Fund)和三次泛音(3rd overtone)。 晶诺威科技产三次泛音晶振系列如下: SMD3225 54MHZ~100MHz SMD5032 40MHZ~150MHz SMD7050 35MHZ~150…时间:2024/03/06

晶振的两种主要振动模式:基频(Fund)与三次泛音(3rd overtone)

关于晶振的两种主要振动模式,晶诺威科技解释如下: 目前,我司产晶振的两种主要振动方式为:基频(Fund)和三次泛音(3rd overtone)。 晶诺威科技产三次泛音晶振系列如下: SMD3225 54MHZ~100MHz SMD5032 40MHZ~150MHz SMD7050 35MHZ~150…时间:2024/03/06 -

; ) 32.768KHz晶振/实时时钟RTC

关于32.768KHz晶振/实时时钟RTC,晶诺威科技说明如下: 32.768KHz晶振是一个标准频率。也有少数应用的频率为25KHz、28KHz、100KHz等。无源晶振以KHz音叉型石英晶体为主,而有源晶振通常以MHz晶体通过分频来实现。 32.768KHz无源晶振主要电气参数: 封装尺寸、负载…时间:2024/03/06

32.768KHz晶振/实时时钟RTC

关于32.768KHz晶振/实时时钟RTC,晶诺威科技说明如下: 32.768KHz晶振是一个标准频率。也有少数应用的频率为25KHz、28KHz、100KHz等。无源晶振以KHz音叉型石英晶体为主,而有源晶振通常以MHz晶体通过分频来实现。 32.768KHz无源晶振主要电气参数: 封装尺寸、负载…时间:2024/03/06 -

; ) 无源晶振在电路中的使用条件

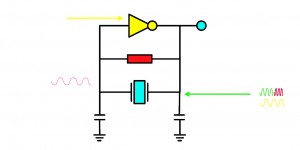

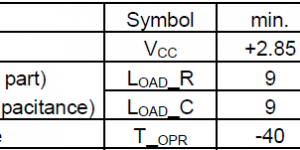

关于无源晶振在电路中的使用条件,晶诺威科技归纳如下: 1、驱动级别(Drive level/DL) 如果晶振的激励功率标注为“100μW max.”,则意味着如果驱动功率太高(如:大于100μW),可能会导致晶体谐振器异常振荡或损坏)。 2、负载电容(Capacitance Load/CL) 要求电…时间:2024/03/05

无源晶振在电路中的使用条件

关于无源晶振在电路中的使用条件,晶诺威科技归纳如下: 1、驱动级别(Drive level/DL) 如果晶振的激励功率标注为“100μW max.”,则意味着如果驱动功率太高(如:大于100μW),可能会导致晶体谐振器异常振荡或损坏)。 2、负载电容(Capacitance Load/CL) 要求电…时间:2024/03/05 -

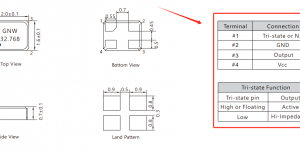

; ) 晶诺威科技产三态功能(Tri-state)晶体振荡器一号脚使用说明

晶诺威科技产三态功能(Tri-state)晶体振荡器一号脚使用说明如下: 如果我司有源晶振规格书中标注其一号脚具备三态功能(Tri-state),其使用说明如下: 当一号脚处于悬空状态(Floating)或为其输入电压为额定电压70%及以上,该晶振信号输出功能激活 当一号脚接地(GND)或为其输入电…时间:2024/03/04

晶诺威科技产三态功能(Tri-state)晶体振荡器一号脚使用说明

晶诺威科技产三态功能(Tri-state)晶体振荡器一号脚使用说明如下: 如果我司有源晶振规格书中标注其一号脚具备三态功能(Tri-state),其使用说明如下: 当一号脚处于悬空状态(Floating)或为其输入电压为额定电压70%及以上,该晶振信号输出功能激活 当一号脚接地(GND)或为其输入电…时间:2024/03/04 -

; ) 1XXB25000MDA温补晶振TCXO2520 25MHz ±0.5ppm规格参数说明

1XXB25000MDA温补晶振TCXO2520 25MHz ±0.5ppm规格参数说明如下 品牌:KDS 类型:温补晶振/TCXO 型号:DSB221SDN 厂家料号:1XXB25000MDA 频率:25MHz 尺寸:TCXO2520 工作温度:-40~+85°C 频率稳定性:±0.5ppm 典型…时间:2024/03/04

1XXB25000MDA温补晶振TCXO2520 25MHz ±0.5ppm规格参数说明

1XXB25000MDA温补晶振TCXO2520 25MHz ±0.5ppm规格参数说明如下 品牌:KDS 类型:温补晶振/TCXO 型号:DSB221SDN 厂家料号:1XXB25000MDA 频率:25MHz 尺寸:TCXO2520 工作温度:-40~+85°C 频率稳定性:±0.5ppm 典型…时间:2024/03/04 -

; ) 无源贴片晶振SMD2016 96MHz 8PF ±10PPM 工作温度-40~85℃

晶诺威科技产无源贴片晶振SMD2016 96MHz 主要电气参数如下: Nominal Frequency 标称频率/中心频率:96MHz Mode/振动模式:AT/Fundamental基频(光刻技术) Frequency Tolerance调整频差:±10 ppm max (at 25°C) L…时间:2024/03/04

无源贴片晶振SMD2016 96MHz 8PF ±10PPM 工作温度-40~85℃

晶诺威科技产无源贴片晶振SMD2016 96MHz 主要电气参数如下: Nominal Frequency 标称频率/中心频率:96MHz Mode/振动模式:AT/Fundamental基频(光刻技术) Frequency Tolerance调整频差:±10 ppm max (at 25°C) L…时间:2024/03/04