-

; ) 芯片手册要求晶振负载电容是8pF是什么意思?

芯片手册要求晶振负载电容是8pF是什么意思? 答:意思是说在晶振选型时,请选择负载电容CL=8pF的石英晶体谐振器,即无源晶振。 解释: 在无源晶振选型时,负载电容CL为无源晶振重要电气参数之一。常见负载电容有6PF、8PF、9PF、12.5PF、9PF、12PF、15PF、18PF、20PF等多种…时间:2023/05/26

芯片手册要求晶振负载电容是8pF是什么意思?

芯片手册要求晶振负载电容是8pF是什么意思? 答:意思是说在晶振选型时,请选择负载电容CL=8pF的石英晶体谐振器,即无源晶振。 解释: 在无源晶振选型时,负载电容CL为无源晶振重要电气参数之一。常见负载电容有6PF、8PF、9PF、12.5PF、9PF、12PF、15PF、18PF、20PF等多种…时间:2023/05/26 -

; ) 造成晶振频偏超差原因,频偏引发的不良影响及解决方案

关于造成晶振频偏超差的原因,晶诺威科技归纳四点如下: 晶振本身电气参数不稳定 晶振的品质因子(Q值)和频率稳定性系数(Δf/f)是影响频率偏差的主要参数。低品质的晶振容易产生较大的频率偏差。 晶振工作环境因素 温度、湿度、气压等环境因素会影响晶体的机械特性,从而导致频率偏差。其中,温度是最主要的影响…时间:2023/05/05

造成晶振频偏超差原因,频偏引发的不良影响及解决方案

关于造成晶振频偏超差的原因,晶诺威科技归纳四点如下: 晶振本身电气参数不稳定 晶振的品质因子(Q值)和频率稳定性系数(Δf/f)是影响频率偏差的主要参数。低品质的晶振容易产生较大的频率偏差。 晶振工作环境因素 温度、湿度、气压等环境因素会影响晶体的机械特性,从而导致频率偏差。其中,温度是最主要的影响…时间:2023/05/05 -

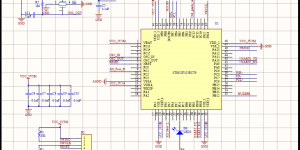

; ) 选择MCU无源晶振及外部器件的简易指南

选择MCU无源晶振及外部器件的简易指南,介绍如下: 第一步:增益裕量(Gainmargin)计算 选择一个晶振(参考MCU的数据手册确定晶振的频率)。 计算晶振的增益裕量(Gainmargin)并检查其是否大于5。 如果Gainmargin <5,说明这不是一个合适的晶振,应当再挑选一个低ES…时间:2023/02/17

选择MCU无源晶振及外部器件的简易指南

选择MCU无源晶振及外部器件的简易指南,介绍如下: 第一步:增益裕量(Gainmargin)计算 选择一个晶振(参考MCU的数据手册确定晶振的频率)。 计算晶振的增益裕量(Gainmargin)并检查其是否大于5。 如果Gainmargin <5,说明这不是一个合适的晶振,应当再挑选一个低ES…时间:2023/02/17 -

; ) 32.768KHz无源晶振的对地电容减小会怎样?

对地电容又叫外接电容或匹配电容,一般情况下,针对32.768KHz无源晶振电路,其可选容值在6PF~22PF之间。对地电容主要应用于无源晶振的振荡电路中,其作用是对晶振的实际输出频率起到一个微调的作用。其原理如下: 1、对地电容容值减小,晶振输出频率偏正向变化。 2、对地电容容值变大,晶振输出频率偏…时间:2023/02/13

32.768KHz无源晶振的对地电容减小会怎样?

对地电容又叫外接电容或匹配电容,一般情况下,针对32.768KHz无源晶振电路,其可选容值在6PF~22PF之间。对地电容主要应用于无源晶振的振荡电路中,其作用是对晶振的实际输出频率起到一个微调的作用。其原理如下: 1、对地电容容值减小,晶振输出频率偏正向变化。 2、对地电容容值变大,晶振输出频率偏…时间:2023/02/13 -

; ) 为何有源晶振频率信号输出端不需要外加匹配电容?

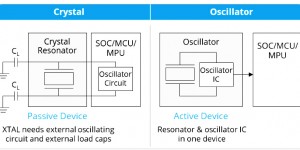

有源晶振是一个经集成后的完整振荡器(Oscillator)。即是说,里面已经有含IC及最佳匹配电容的振荡电路,信号输出端无需再外加匹配电容。有源晶振的特点是信号稳定度高且精准。在信号输出之前,正弦波已完成自身到方波的整形过程,有源晶振的输出信号主要为直接对应数字电路信号的方波(CMOS)。 无源晶振…时间:2022/12/29

为何有源晶振频率信号输出端不需要外加匹配电容?

有源晶振是一个经集成后的完整振荡器(Oscillator)。即是说,里面已经有含IC及最佳匹配电容的振荡电路,信号输出端无需再外加匹配电容。有源晶振的特点是信号稳定度高且精准。在信号输出之前,正弦波已完成自身到方波的整形过程,有源晶振的输出信号主要为直接对应数字电路信号的方波(CMOS)。 无源晶振…时间:2022/12/29 -

; ) 12.5PF的晶体匹配电容是多少PF?

匹配电容的变化对晶体输出频率的影响: 匹配电容容值增加,晶体输出频率降低。 匹配电容容值减小,晶体输出频率升高。 如果晶体负载电容CL为12.5PF,晶诺威科技建议匹配电容在15~18PF之间取值。但在晶体实际电路应用中,也有匹配22PF为最佳的情况,这主要归因于电路板本身之间的差异。 匹配电容对晶…时间:2022/12/14

12.5PF的晶体匹配电容是多少PF?

匹配电容的变化对晶体输出频率的影响: 匹配电容容值增加,晶体输出频率降低。 匹配电容容值减小,晶体输出频率升高。 如果晶体负载电容CL为12.5PF,晶诺威科技建议匹配电容在15~18PF之间取值。但在晶体实际电路应用中,也有匹配22PF为最佳的情况,这主要归因于电路板本身之间的差异。 匹配电容对晶…时间:2022/12/14 -

; ) 晶振的负载电容不等于其匹配电容

负载电容CL是电路中跨接无源晶振两端的总的有效电容,它并不是指无源晶振外接的匹配电容。负载电容CL主要影响负载谐振频率和等效负载谐振电阻,与无源晶振⼀起决定振荡器电路的⼯作频率。通过调整负载电容的大小,就可以将振荡器的⼯作频率微调到靠近标称值。 负载电容CL是⽆源晶振⾮常重要的参数,因为⽆源晶振属于…时间:2022/07/31

晶振的负载电容不等于其匹配电容

负载电容CL是电路中跨接无源晶振两端的总的有效电容,它并不是指无源晶振外接的匹配电容。负载电容CL主要影响负载谐振频率和等效负载谐振电阻,与无源晶振⼀起决定振荡器电路的⼯作频率。通过调整负载电容的大小,就可以将振荡器的⼯作频率微调到靠近标称值。 负载电容CL是⽆源晶振⾮常重要的参数,因为⽆源晶振属于…时间:2022/07/31 -

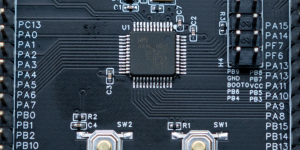

; ) 有源晶振和无源晶振电路差异及应用注意事项

关于有源晶振和无源晶振电路差异,晶诺威科技解释如下: 有源晶振不需要匹配电容起振便可直接工作,从逻辑上讲,直接上电即可起振; 无源晶振需要在起振电路中匹配合适的电容(启动电容)才能正常起振。在起振电路中,在没有外接匹配电容的情况下,无源晶振也可以起振,但容易发生频偏超差问题,主要体现为“偏正”。 晶…时间:2022/05/19

有源晶振和无源晶振电路差异及应用注意事项

关于有源晶振和无源晶振电路差异,晶诺威科技解释如下: 有源晶振不需要匹配电容起振便可直接工作,从逻辑上讲,直接上电即可起振; 无源晶振需要在起振电路中匹配合适的电容(启动电容)才能正常起振。在起振电路中,在没有外接匹配电容的情况下,无源晶振也可以起振,但容易发生频偏超差问题,主要体现为“偏正”。 晶…时间:2022/05/19 -

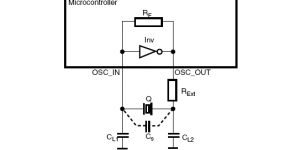

; ) 无源晶振振荡条件与接地电容之间的关系

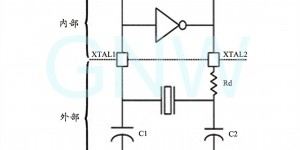

关于无源晶振振荡条件与接地电容之间的关系,晶诺威科技介绍如下: 各种逻辑芯片的无源晶振引脚可以等效为电容三点式振荡器。 无源晶振引脚的内部通常是一个反相器, 或者是奇数个反相器串联。在无源晶振输出引脚 XO 和晶振输入引脚 XI 之间用一个电阻连接, 对于 CMOS 芯片通常是数 M 到数十M 欧之…时间:2022/05/16

无源晶振振荡条件与接地电容之间的关系

关于无源晶振振荡条件与接地电容之间的关系,晶诺威科技介绍如下: 各种逻辑芯片的无源晶振引脚可以等效为电容三点式振荡器。 无源晶振引脚的内部通常是一个反相器, 或者是奇数个反相器串联。在无源晶振输出引脚 XO 和晶振输入引脚 XI 之间用一个电阻连接, 对于 CMOS 芯片通常是数 M 到数十M 欧之…时间:2022/05/16 -

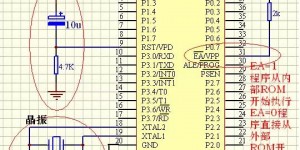

; ) 8MHz无源晶振典型电路:8MHz晶振需要匹配多大电容?

(贴片式无源晶振SMD3225-4 pads) 晶诺威科技生产的贴片无源晶振8M常见负载电容CL为12PF和20PF,建议如下: 当晶振负载电容CL=12PF时,建议匹配电容在15-18PF之间。 当晶振负载电容CL=20PF时,建议匹配电容在27-33PF之间。 由以上可见,8MHz…时间:2022/05/11

8MHz无源晶振典型电路:8MHz晶振需要匹配多大电容?

(贴片式无源晶振SMD3225-4 pads) 晶诺威科技生产的贴片无源晶振8M常见负载电容CL为12PF和20PF,建议如下: 当晶振负载电容CL=12PF时,建议匹配电容在15-18PF之间。 当晶振负载电容CL=20PF时,建议匹配电容在27-33PF之间。 由以上可见,8MHz…时间:2022/05/11