-

; ) 展频晶振(SPREAD SPECTRUM)SG9101系列规格参数

展频晶振(SPREAD SPECTRUM)SG9101系列规格参数介绍如下: Applications 展频晶振应用 SATA, Ethernet, PCI express, Video, Wireless,Computing, Storage, Networking, Telecom, Indus…时间:2022/11/29

展频晶振(SPREAD SPECTRUM)SG9101系列规格参数

展频晶振(SPREAD SPECTRUM)SG9101系列规格参数介绍如下: Applications 展频晶振应用 SATA, Ethernet, PCI express, Video, Wireless,Computing, Storage, Networking, Telecom, Indus…时间:2022/11/29 -

; ) EPSON SPREAD SPECTRUM/爱普生展频晶振SG9101规格及使用说明

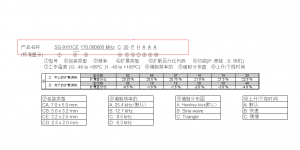

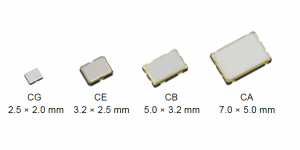

EPSON SPREAD SPECTRUM/爱普生展频晶振SG9101规格参数说明如下: 扩频(Spread Spectrum,SS)是将传输信号的频谱(spectrum)打散到较其原始带宽更宽的一种通信技术,常用于无线通信领域。 Product Number 爱普生展频晶振SG9101产品编码 S…时间:2022/09/07

EPSON SPREAD SPECTRUM/爱普生展频晶振SG9101规格及使用说明

EPSON SPREAD SPECTRUM/爱普生展频晶振SG9101规格参数说明如下: 扩频(Spread Spectrum,SS)是将传输信号的频谱(spectrum)打散到较其原始带宽更宽的一种通信技术,常用于无线通信领域。 Product Number 爱普生展频晶振SG9101产品编码 S…时间:2022/09/07 -

; ) 晶振抗干扰电路:电源,信号线,GND及隔离区设计说明

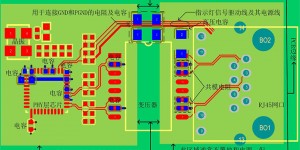

(晶振抗干扰电路:关于电源,信号线,GND及隔离区图示) 晶振抗干扰电路设计时,请注意以下六点: 1、在晶振布线时,尽量将晶振靠近芯片方式、缩短布线长度,匹配电容也一样 2、晶振走线要直 3、晶振走线不能有过孔 4、晶振位置不要靠近高压,大电流的电源走线 5、有源晶振一般比无源晶振抗干扰能力更强,因…时间:2022/05/31

晶振抗干扰电路:电源,信号线,GND及隔离区设计说明

(晶振抗干扰电路:关于电源,信号线,GND及隔离区图示) 晶振抗干扰电路设计时,请注意以下六点: 1、在晶振布线时,尽量将晶振靠近芯片方式、缩短布线长度,匹配电容也一样 2、晶振走线要直 3、晶振走线不能有过孔 4、晶振位置不要靠近高压,大电流的电源走线 5、有源晶振一般比无源晶振抗干扰能力更强,因…时间:2022/05/31 -

; ) 如何减少辐射对时钟信号的干扰?

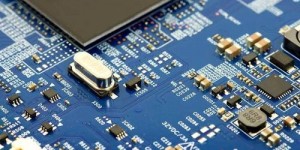

晶振在电路板中起到提供时钟信号的关键作用。我们在布线时应该优先设计晶振的位置,以规避时钟受周围信号干扰而导致电路板上电不良之隐患。 1、有正弦波输出的贴片晶振,输出负载为10k;如果10k的负载能力不够,必须加缓冲电路,使PLL的参考与单片机的时钟相隔离; 2、晶振输出到PLL的信号线不能长,否则再…时间:2020/10/13

如何减少辐射对时钟信号的干扰?

晶振在电路板中起到提供时钟信号的关键作用。我们在布线时应该优先设计晶振的位置,以规避时钟受周围信号干扰而导致电路板上电不良之隐患。 1、有正弦波输出的贴片晶振,输出负载为10k;如果10k的负载能力不够,必须加缓冲电路,使PLL的参考与单片机的时钟相隔离; 2、晶振输出到PLL的信号线不能长,否则再…时间:2020/10/13