-

; ) 为什么12pF负载的晶振外接6.8pF电容?

为什么12pF负载的晶振外接6.8pF电容? 对于负载电容( CL = 12pF ) 的晶振,外接 6.8pF 的电容通常是偏小的,但具体情况要看是“对地电容”还是“负载电容”。 为了让你更清楚,晶诺威科技分析三种情况如下: 1、 如果 6.8pF 是指“两个外接对地电容”的容值 这是最常见的情况。…时间:2026/04/23

为什么12pF负载的晶振外接6.8pF电容?

为什么12pF负载的晶振外接6.8pF电容? 对于负载电容( CL = 12pF ) 的晶振,外接 6.8pF 的电容通常是偏小的,但具体情况要看是“对地电容”还是“负载电容”。 为了让你更清楚,晶诺威科技分析三种情况如下: 1、 如果 6.8pF 是指“两个外接对地电容”的容值 这是最常见的情况。…时间:2026/04/23 -

; ) 无源晶振(晶体谐振器)两个外接电容不一样可以吗?

无源晶振(晶体谐振器)两个外接电容不一样可以吗? 答:在绝大多数情况下,不建议将晶振的两个外接电容设计成不一样的,最好使用相同容值的电容。 虽然在某些特定条件下,使用不等值电容是一种调试技巧,但这属于非常规操作,需要谨慎对待。 关于外接电容选择问题,晶诺威科技详解如下: 一、使用相等电…时间:2026/04/05

无源晶振(晶体谐振器)两个外接电容不一样可以吗?

无源晶振(晶体谐振器)两个外接电容不一样可以吗? 答:在绝大多数情况下,不建议将晶振的两个外接电容设计成不一样的,最好使用相同容值的电容。 虽然在某些特定条件下,使用不等值电容是一种调试技巧,但这属于非常规操作,需要谨慎对待。 关于外接电容选择问题,晶诺威科技详解如下: 一、使用相等电…时间:2026/04/05 -

; ) 为何相同频率的晶振,负载电容pF值却不一样?

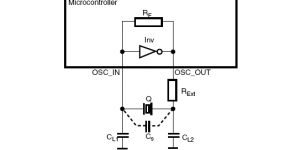

无源晶振皮尔斯振荡电路 为何相同频率的晶振,负载电容PF值却不一样? 答:“相同频率的晶振,其标称负载电容(Load Capacitance, CL)值可以不同”是完全正常且常见的现象。这并不意味着晶振有问题,而是反映了不同的设计选择和匹配要求。 负载电容(CL)是晶振外部需要连接的两个电容(CL1…时间:2026/03/03

为何相同频率的晶振,负载电容pF值却不一样?

无源晶振皮尔斯振荡电路 为何相同频率的晶振,负载电容PF值却不一样? 答:“相同频率的晶振,其标称负载电容(Load Capacitance, CL)值可以不同”是完全正常且常见的现象。这并不意味着晶振有问题,而是反映了不同的设计选择和匹配要求。 负载电容(CL)是晶振外部需要连接的两个电容(CL1…时间:2026/03/03 -

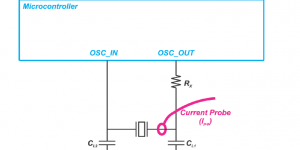

; ) 芯片/单片机/MCU/CPU无源晶振输入输出定义

芯片/单片机/MCU/CPU无源晶振输入输出常见命名,举例如下: STMicroelectronics(意法半导体):OSC_IN 和 OSC_OUT NXP(恩智浦):XTALI 和 XTALO Microchip(微芯):OSC1 和 OSC2 皮尔斯振荡电路 无源晶振(Crystal) 角色:…时间:2026/02/12

芯片/单片机/MCU/CPU无源晶振输入输出定义

芯片/单片机/MCU/CPU无源晶振输入输出常见命名,举例如下: STMicroelectronics(意法半导体):OSC_IN 和 OSC_OUT NXP(恩智浦):XTALI 和 XTALO Microchip(微芯):OSC1 和 OSC2 皮尔斯振荡电路 无源晶振(Crystal) 角色:…时间:2026/02/12 -

; ) 晶振的CL代表用多大的电容吗?

晶振的CL代表用多大的电容吗? 答:这是一个很常见的误解。晶振的CL(Load Capacitance,负载电容)并不是指需要外接多大的具体某个电容,而是指晶振在设计和出厂校准频率时所依据的一个关键负载电容参数值。电路必须匹配这个值,晶振才能工作在标称频率上。 简单来说:CL是无源晶振的“身份证”参…时间:2026/01/12

晶振的CL代表用多大的电容吗?

晶振的CL代表用多大的电容吗? 答:这是一个很常见的误解。晶振的CL(Load Capacitance,负载电容)并不是指需要外接多大的具体某个电容,而是指晶振在设计和出厂校准频率时所依据的一个关键负载电容参数值。电路必须匹配这个值,晶振才能工作在标称频率上。 简单来说:CL是无源晶振的“身份证”参…时间:2026/01/12 -

; ) RTC晶振32.768KHz负载电容CL选用12.5pF还是7pF?

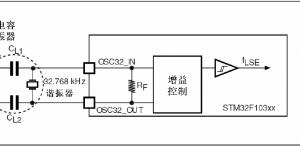

RTC晶振32.768KHz负载电容CL选用12.5pF还是7pF? 答:RTC晶振负载电容CL大小由芯片决定,请根据芯片数据手册取值。若无源晶振的负载电容CL选择错误,可能造成晶振不起振。 RTC晶振32.768KHz负载电容CL值常见有:7pF、9pF、12.5pF等,不同负载电容CL应匹配不同…时间:2025/12/25

RTC晶振32.768KHz负载电容CL选用12.5pF还是7pF?

RTC晶振32.768KHz负载电容CL选用12.5pF还是7pF? 答:RTC晶振负载电容CL大小由芯片决定,请根据芯片数据手册取值。若无源晶振的负载电容CL选择错误,可能造成晶振不起振。 RTC晶振32.768KHz负载电容CL值常见有:7pF、9pF、12.5pF等,不同负载电容CL应匹配不同…时间:2025/12/25 -

; ) 无源晶振(Crystal Resonator)内部有电容吗?

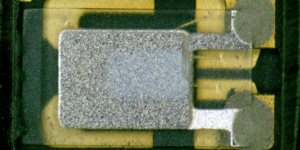

贴片式无源晶振(Crystal Resonator)内部解剖图 无源晶振(Crystal Resonator)内部有电容吗? 答:无源晶振(Crystal Resonator)内部没有电容。 晶诺威科技详解如下: 1、 无源晶振的本质 无源晶振的核心是一块经过精密切割并镀上电极的石英晶体片。它利用的…时间:2025/09/11

无源晶振(Crystal Resonator)内部有电容吗?

贴片式无源晶振(Crystal Resonator)内部解剖图 无源晶振(Crystal Resonator)内部有电容吗? 答:无源晶振(Crystal Resonator)内部没有电容。 晶诺威科技详解如下: 1、 无源晶振的本质 无源晶振的核心是一块经过精密切割并镀上电极的石英晶体片。它利用的…时间:2025/09/11 -

; ) Some common questions about Quartz Crystal

Some common questions about Quartz Crystal 1. No signal output from the crystal on oscillation circuit? If there is no signal output measured by two t…时间:2025/08/26

Some common questions about Quartz Crystal

Some common questions about Quartz Crystal 1. No signal output from the crystal on oscillation circuit? If there is no signal output measured by two t…时间:2025/08/26 -

; ) 晶振的起振电容太大了会有什么影响?

晶振的起振电容太大了会有什么影响? 答:会造成晶振频率偏负向、起振慢甚至停振。 晶诺威科技进一步解释如下: 晶振的起振电容(外接电容,通常为CL1和CL2)过大会对电路产生以下影响: 1、 频率偏移 起振电容过大会导致晶振输出频率低于标称频率。对时序敏感的电路(如MCU、通信模块),频率偏差可能导致…时间:2025/06/10

晶振的起振电容太大了会有什么影响?

晶振的起振电容太大了会有什么影响? 答:会造成晶振频率偏负向、起振慢甚至停振。 晶诺威科技进一步解释如下: 晶振的起振电容(外接电容,通常为CL1和CL2)过大会对电路产生以下影响: 1、 频率偏移 起振电容过大会导致晶振输出频率低于标称频率。对时序敏感的电路(如MCU、通信模块),频率偏差可能导致…时间:2025/06/10 -

; ) 晶体谐振器的起振电容通常取值范围是多少?

晶体谐振器的起振电容通常取值范围是多少? 答:晶体谐振器(无源晶振)起振电容一般在几皮法(pF)到几十皮法之间,常用范围为10pF至30pF。 注意: 1、具体值需根据晶体的负载电容要求选择。 2、实际应用中,需根据电路设计和元件参数选择合适的电容值,必要时通过实验调整以达到最佳效果。时间:2025/04/20

晶体谐振器的起振电容通常取值范围是多少?

晶体谐振器的起振电容通常取值范围是多少? 答:晶体谐振器(无源晶振)起振电容一般在几皮法(pF)到几十皮法之间,常用范围为10pF至30pF。 注意: 1、具体值需根据晶体的负载电容要求选择。 2、实际应用中,需根据电路设计和元件参数选择合适的电容值,必要时通过实验调整以达到最佳效果。时间:2025/04/20