-

; ) 时钟偏差/倾斜Clock Skew与VCXO压控晶振的Voltage Control

Clock Skew是影响时钟信号稳定性的主要因素之一。 若VCXO额定输入电压为5V,当实际输入电压为2.5V时,晶振输出频率为中心频率。 电源的表现形式也可看做为波形的一种。当占空比为0时,实质为直流电。在VCXO实际工作中,由于时钟源到达不同寄存器所经历路径的驱动和负载的不同,时钟边沿的位置有…时间:2022/07/07

时钟偏差/倾斜Clock Skew与VCXO压控晶振的Voltage Control

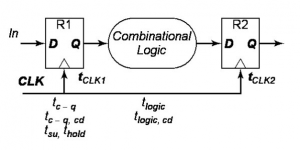

Clock Skew是影响时钟信号稳定性的主要因素之一。 若VCXO额定输入电压为5V,当实际输入电压为2.5V时,晶振输出频率为中心频率。 电源的表现形式也可看做为波形的一种。当占空比为0时,实质为直流电。在VCXO实际工作中,由于时钟源到达不同寄存器所经历路径的驱动和负载的不同,时钟边沿的位置有…时间:2022/07/07 -

; ) 在晶振应用中的时钟偏移(skew)和时钟抖动(jitter)分别指什么?

在晶振应用中的时钟偏移(skew)和时钟抖动 时钟偏移(skew) 指同样的时钟产生的多个子时钟信号之间的延时差异。skew通常是时钟相位上的不确定。由于时钟源到达不同寄存器所经历路径的驱动和负载的不同,时钟边沿的位置有所差异,因此就带来了skew。完成布局布线后,物理路径延时是固定的,所以在设计中…时间:2021/08/22

在晶振应用中的时钟偏移(skew)和时钟抖动(jitter)分别指什么?

在晶振应用中的时钟偏移(skew)和时钟抖动 时钟偏移(skew) 指同样的时钟产生的多个子时钟信号之间的延时差异。skew通常是时钟相位上的不确定。由于时钟源到达不同寄存器所经历路径的驱动和负载的不同,时钟边沿的位置有所差异,因此就带来了skew。完成布局布线后,物理路径延时是固定的,所以在设计中…时间:2021/08/22 -

; ) 如何控制晶振时钟信号的偏移skew?

晶振时钟信号偏移skew概念 整个芯片中时钟信号到达各级电路的时间差即为时钟偏移skew。 造成晶振时钟信号偏移skew的根本原因 短路径问题:即逻辑单元速度快,输出数据比时钟传播到下个逻辑单元还要快,就会造成数据丢失,从而导致逻辑功能出错。 如何控制晶振时钟信号的偏移skew?建议有以下五点: 添…时间:2021/08/13

如何控制晶振时钟信号的偏移skew?

晶振时钟信号偏移skew概念 整个芯片中时钟信号到达各级电路的时间差即为时钟偏移skew。 造成晶振时钟信号偏移skew的根本原因 短路径问题:即逻辑单元速度快,输出数据比时钟传播到下个逻辑单元还要快,就会造成数据丢失,从而导致逻辑功能出错。 如何控制晶振时钟信号的偏移skew?建议有以下五点: 添…时间:2021/08/13