-

; ) 晶振的10个关键参数是什么?

关于晶振的10个关键参数,晶诺威科技归纳如下: 1、工作频率 晶振的频率范围一般在1到125MHz之间。但也有诸如通用的32.768kHz钟表晶体那样的特殊低频晶体。工作频率一般按工作温度25°C时给出。 2、频率精度:1PPM=1/1,000,000 频率精度也称频率容限,该指标度量晶振实际频率于…时间:2022/11/04

晶振的10个关键参数是什么?

关于晶振的10个关键参数,晶诺威科技归纳如下: 1、工作频率 晶振的频率范围一般在1到125MHz之间。但也有诸如通用的32.768kHz钟表晶体那样的特殊低频晶体。工作频率一般按工作温度25°C时给出。 2、频率精度:1PPM=1/1,000,000 频率精度也称频率容限,该指标度量晶振实际频率于…时间:2022/11/04 -

; ) 晶振功耗,晶振起振时间与晶振相噪

我们在追求晶振输出频率高精度及高稳定性的同时,也对其功耗、起振时间及相噪等三方面提出了更高要求。 显而易见,当前智能化电子产品呈现高精密化及网络通信设备呈现数据高速化等趋势。具备小尺寸和低功耗的晶振适合在移动设备和穿戴设备中使用,而该类电子产品的特点为:电源电压、电流、体积、功耗相应减小、驱动能力变…时间:2022/07/01

晶振功耗,晶振起振时间与晶振相噪

我们在追求晶振输出频率高精度及高稳定性的同时,也对其功耗、起振时间及相噪等三方面提出了更高要求。 显而易见,当前智能化电子产品呈现高精密化及网络通信设备呈现数据高速化等趋势。具备小尺寸和低功耗的晶振适合在移动设备和穿戴设备中使用,而该类电子产品的特点为:电源电压、电流、体积、功耗相应减小、驱动能力变…时间:2022/07/01 -

; ) 造成晶振相位噪声的原因有哪些?

关于晶振的相位噪声phase noise概念,晶诺威科技解释如下: 表示在波形的频域中,由相位(频率)的快速,短期,随机波动组成。这是由时域不稳定性(抖动)引起的。 确保不要将相位噪声与抖动混淆。 抖动jitter是一种描述晶振在时域中的稳定性的方法。它将所有噪声源组合在一起,并显示它们相对于时间的…时间:2021/09/10

造成晶振相位噪声的原因有哪些?

关于晶振的相位噪声phase noise概念,晶诺威科技解释如下: 表示在波形的频域中,由相位(频率)的快速,短期,随机波动组成。这是由时域不稳定性(抖动)引起的。 确保不要将相位噪声与抖动混淆。 抖动jitter是一种描述晶振在时域中的稳定性的方法。它将所有噪声源组合在一起,并显示它们相对于时间的…时间:2021/09/10 -

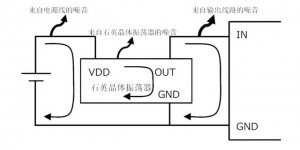

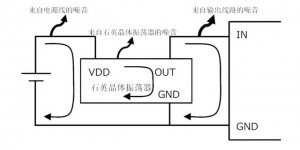

; ) 晶振周围相噪phase noise源及相噪对策

(石英晶体振荡器周围可产生相噪的电路) 相噪phase noise发生源分为主要三大类: (1)来自电源线的相噪:在晶振工作过程中,电源线中将产生脉动。电源线起到天线的作用脉动作为相噪释放。防止电源相噪时重要的是如何阻止或吸收晶振所产生的脉动流入电源线。为此而采取的对策可防止其它元器件所产生的外來相…时间:2021/08/13

晶振周围相噪phase noise源及相噪对策

(石英晶体振荡器周围可产生相噪的电路) 相噪phase noise发生源分为主要三大类: (1)来自电源线的相噪:在晶振工作过程中,电源线中将产生脉动。电源线起到天线的作用脉动作为相噪释放。防止电源相噪时重要的是如何阻止或吸收晶振所产生的脉动流入电源线。为此而采取的对策可防止其它元器件所产生的外來相…时间:2021/08/13 -

; ) 减少晶振周边电路相噪phase noise的两项最重要方法

晶振周围电路的合适设计对减少相噪noise极为重要。只要电路设计妥善适宜,即可很大程度避免相噪问题,从而充分发挥电子元器件本身所具有的性能。 减少晶振周边电路相噪的方法主要有以下两点: 缩短输岀线路 输出线路是电路中最容易释放相噪的部分。为此,在设计电路图案之际,应当最优先设计输岀线路部分,采用长度…时间:2021/08/06

减少晶振周边电路相噪phase noise的两项最重要方法

晶振周围电路的合适设计对减少相噪noise极为重要。只要电路设计妥善适宜,即可很大程度避免相噪问题,从而充分发挥电子元器件本身所具有的性能。 减少晶振周边电路相噪的方法主要有以下两点: 缩短输岀线路 输出线路是电路中最容易释放相噪的部分。为此,在设计电路图案之际,应当最优先设计输岀线路部分,采用长度…时间:2021/08/06 -

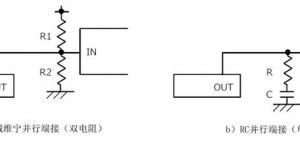

; ) 如何通过串联电阻降低晶振相噪phase noise,避免输出波形output waveform失真?

串联电阻降低晶振相噪(phase noise)避免输出波形(output waveform)失真方法介绍 主要分为连接串联电阻与连接终端电阻两部分: 连接串联电阻: 晶振连接输入对象的元器件时,通常产生过冲、下冲或振铃等波形变形。这些变形的波形中含有振荡频率的约3-7倍的射频成份,将引发相噪,所以必…时间:2021/08/05

如何通过串联电阻降低晶振相噪phase noise,避免输出波形output waveform失真?

串联电阻降低晶振相噪(phase noise)避免输出波形(output waveform)失真方法介绍 主要分为连接串联电阻与连接终端电阻两部分: 连接串联电阻: 晶振连接输入对象的元器件时,通常产生过冲、下冲或振铃等波形变形。这些变形的波形中含有振荡频率的约3-7倍的射频成份,将引发相噪,所以必…时间:2021/08/05