-

; ) 造成晶振频偏超差原因,频偏引发的不良影响及解决方案

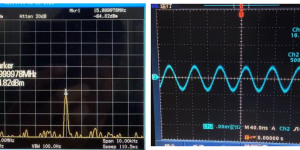

关于造成晶振频偏超差的原因,晶诺威科技归纳四点如下: 晶振本身电气参数不稳定 晶振的品质因子(Q值)和频率稳定性系数(Δf/f)是影响频率偏差的主要参数。低品质的晶振容易产生较大的频率偏差。 晶振工作环境因素 温度、湿度、气压等环境因素会影响晶体的机械特性,从而导致频率偏差。其中,温度是最主要的影响…时间:2023/05/05

造成晶振频偏超差原因,频偏引发的不良影响及解决方案

关于造成晶振频偏超差的原因,晶诺威科技归纳四点如下: 晶振本身电气参数不稳定 晶振的品质因子(Q值)和频率稳定性系数(Δf/f)是影响频率偏差的主要参数。低品质的晶振容易产生较大的频率偏差。 晶振工作环境因素 温度、湿度、气压等环境因素会影响晶体的机械特性,从而导致频率偏差。其中,温度是最主要的影响…时间:2023/05/05 -

; ) 关于晶振ESR(等效阻抗)太大导致晶振不起振问题

关于晶振ESR(等效阻抗)太大导致晶振不起振问题,晶诺威科技解释如下: 在无源晶振起振电路中,电路负性阻抗一般要在晶振ESR(等效阻抗)的5倍以上才能保障其正常起振。但是如果因晶振品质不合格,导致其ESR过大,也会造成晶振起振困难或不起振。 晶诺威科技产SMD7050晶体谐振器ESR(等效阻抗)说明…时间:2023/04/15

关于晶振ESR(等效阻抗)太大导致晶振不起振问题

关于晶振ESR(等效阻抗)太大导致晶振不起振问题,晶诺威科技解释如下: 在无源晶振起振电路中,电路负性阻抗一般要在晶振ESR(等效阻抗)的5倍以上才能保障其正常起振。但是如果因晶振品质不合格,导致其ESR过大,也会造成晶振起振困难或不起振。 晶诺威科技产SMD7050晶体谐振器ESR(等效阻抗)说明…时间:2023/04/15 -

; ) 晶振频偏主要原因之一:负载电容与电容匹配存在差异

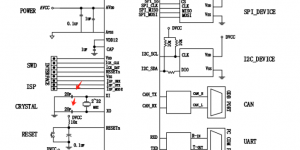

负载电容(CL) 负载电容(CL)是无源晶振的必选电气参数之一。关于该参数的选取,请严格遵循IC手册中晶振相关说明。 在振荡电路中,如果无源晶振两端的等效电容和标称负载电容存在差异,该晶振实际输出的频率将会与标称工作频率产生偏差,这种偏差被称之为“频率偏差”,简称“频偏”。这种偏差越小越好。 电容匹…时间:2023/03/03

晶振频偏主要原因之一:负载电容与电容匹配存在差异

负载电容(CL) 负载电容(CL)是无源晶振的必选电气参数之一。关于该参数的选取,请严格遵循IC手册中晶振相关说明。 在振荡电路中,如果无源晶振两端的等效电容和标称负载电容存在差异,该晶振实际输出的频率将会与标称工作频率产生偏差,这种偏差被称之为“频率偏差”,简称“频偏”。这种偏差越小越好。 电容匹…时间:2023/03/03 -

; ) 晶振频差Frequency Tolerance 和晶振频偏Frequency Deviation

关于晶振频差Frequency Tolerance 和晶振频偏Frequency Deviation,解释如下: 晶振频差(英文:Frequency Tolerance) 在晶振数据手册中,“频差”指的是晶振的调整频差,具体指晶振频率与晶振本身中心频率的差值。在实际电路应用中,晶振被设计为可以处于该…时间:2022/11/09

晶振频差Frequency Tolerance 和晶振频偏Frequency Deviation

关于晶振频差Frequency Tolerance 和晶振频偏Frequency Deviation,解释如下: 晶振频差(英文:Frequency Tolerance) 在晶振数据手册中,“频差”指的是晶振的调整频差,具体指晶振频率与晶振本身中心频率的差值。在实际电路应用中,晶振被设计为可以处于该…时间:2022/11/09 -

; ) 晶振初始频率精度是什么意思?

晶振初始频率精度:又被称为调整频差、频率容限、频率容差、晶振精度、频偏 英文:Frequency Tolerance Frequency Tolerance means the maximum permissible departure by the center frequency of the …时间:2022/10/26

晶振初始频率精度是什么意思?

晶振初始频率精度:又被称为调整频差、频率容限、频率容差、晶振精度、频偏 英文:Frequency Tolerance Frequency Tolerance means the maximum permissible departure by the center frequency of the …时间:2022/10/26 -

; ) 晶振频偏过大怎么办?

晶振输出频率偏差过大的影响 设备性能下降: 当晶振频率偏差过大,会导致系统时钟信号的准确性和稳定性受到影响,进而影响整个设备的性能。例如,在智能手机或平板电脑上,晶振偏差可能导致应用程序的反应时间变慢,影响用户体验。 电路模块故障: 晶振频率偏差可能导致某些电路模块无法正常工作。例如,某些无线通信…时间:2022/09/27

晶振频偏过大怎么办?

晶振输出频率偏差过大的影响 设备性能下降: 当晶振频率偏差过大,会导致系统时钟信号的准确性和稳定性受到影响,进而影响整个设备的性能。例如,在智能手机或平板电脑上,晶振偏差可能导致应用程序的反应时间变慢,影响用户体验。 电路模块故障: 晶振频率偏差可能导致某些电路模块无法正常工作。例如,某些无线通信…时间:2022/09/27 -

; ) 12MHz无源晶振需要多大PF外接电容?

若12MHz无源晶振负载CL(标称电容)=20PF,考虑电路板存在4~6PF杂散电容的条件下,建议为其两个频率管脚分别配27~33PF的等值电容。27~33PF仅为理论值。若需要晶振输出频率更为精准的话,需要上电测试晶振实际输出频率与标称频率之间的偏差(Frequency Deviation),并根…时间:2022/07/27

12MHz无源晶振需要多大PF外接电容?

若12MHz无源晶振负载CL(标称电容)=20PF,考虑电路板存在4~6PF杂散电容的条件下,建议为其两个频率管脚分别配27~33PF的等值电容。27~33PF仅为理论值。若需要晶振输出频率更为精准的话,需要上电测试晶振实际输出频率与标称频率之间的偏差(Frequency Deviation),并根…时间:2022/07/27 -

; ) 无源晶振输出频率有偏差是什么原因?怎么解决?

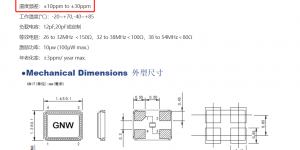

首先,无源晶振自身存在不同的频率精度及误差。若在实际应用中发现无源晶振输出频率偏差过大,不能满足需求,建议首先对无源晶振个体进行测试。一般情况下,无源晶振的频率精度一致性通常会小于±10ppm。 在此,请关注以下指标(可选): 调整频差:±10ppm、±20ppm、±30ppm 注:调整频差通常指的…时间:2022/07/18

无源晶振输出频率有偏差是什么原因?怎么解决?

首先,无源晶振自身存在不同的频率精度及误差。若在实际应用中发现无源晶振输出频率偏差过大,不能满足需求,建议首先对无源晶振个体进行测试。一般情况下,无源晶振的频率精度一致性通常会小于±10ppm。 在此,请关注以下指标(可选): 调整频差:±10ppm、±20ppm、±30ppm 注:调整频差通常指的…时间:2022/07/18 -

; ) 关于晶振受热起振或受热停振的问题

受热起振或受热停振,都说明晶振的工作不稳定。 那么,为何在电路中,晶振会因工作温度的变化而出现频率不稳定的现象呢? 原因有二:一则是晶振本身品质不良;二则是振荡电路出现问题。 首先,当晶振本身品质不良,常见为晶振电阻在某个高温区域出现跳变,主要是突然变大时,晶振将会停振。另外一种现象是晶振低温停振。…时间:2022/07/05

关于晶振受热起振或受热停振的问题

受热起振或受热停振,都说明晶振的工作不稳定。 那么,为何在电路中,晶振会因工作温度的变化而出现频率不稳定的现象呢? 原因有二:一则是晶振本身品质不良;二则是振荡电路出现问题。 首先,当晶振本身品质不良,常见为晶振电阻在某个高温区域出现跳变,主要是突然变大时,晶振将会停振。另外一种现象是晶振低温停振。…时间:2022/07/05 -

; ) 晶振频差、晶振频偏和晶振跳频的差别

关于晶振频差、晶振频偏和晶振跳频的差别,解释如下: 晶振频差 频差指的是晶振的一个电气参数,如上图所示。 包括常温25℃下及工作温度范围内的频率偏差程度。一般情况下,晶振规格书中都有注明调整频差和温度频差。 晶振频偏 频偏可以指晶振在实际工作中偏离中心频率的程度,也可以指晶振偏离允许频差范围的程度。…时间:2022/06/15

晶振频差、晶振频偏和晶振跳频的差别

关于晶振频差、晶振频偏和晶振跳频的差别,解释如下: 晶振频差 频差指的是晶振的一个电气参数,如上图所示。 包括常温25℃下及工作温度范围内的频率偏差程度。一般情况下,晶振规格书中都有注明调整频差和温度频差。 晶振频偏 频偏可以指晶振在实际工作中偏离中心频率的程度,也可以指晶振偏离允许频差范围的程度。…时间:2022/06/15