-

; ) 晶振接地与不接地的区别是什么?

晶振接地与不接地的区别是什么? 答:晶振的接地处理,直接关系到整个系统的电磁兼容性和信号稳定性。 简单来说:如果应用对EMC有要求,晶振的外壳必须接地,而且不是随便接上就行,必须接好。 不接地或接地不良,往往是导致EMC辐射超标和系统不稳定的常见原因之一。 1. 原理:为什么晶振外壳需要接地? 晶振…时间:2026/03/30

晶振接地与不接地的区别是什么?

晶振接地与不接地的区别是什么? 答:晶振的接地处理,直接关系到整个系统的电磁兼容性和信号稳定性。 简单来说:如果应用对EMC有要求,晶振的外壳必须接地,而且不是随便接上就行,必须接好。 不接地或接地不良,往往是导致EMC辐射超标和系统不稳定的常见原因之一。 1. 原理:为什么晶振外壳需要接地? 晶振…时间:2026/03/30 -

; ) 关于网口晶振25MHz/50MHz辐射超标问题的建议

(晶振辐射超标) 网口EMC辐射超标是硬件设计中非常经典的难题。它的根源往往是一个“干扰源”加上一条“发射天线”的组合——板上的高频噪声(比如晶振的谐波)通过网口这个路径,以共模电流的形式耦合到网线上,而网线本身就是一根高效的 antenna,将噪声辐射出去。 简单来说,网口晶振(如:25MHz/5…时间:2025/11/13

关于网口晶振25MHz/50MHz辐射超标问题的建议

(晶振辐射超标) 网口EMC辐射超标是硬件设计中非常经典的难题。它的根源往往是一个“干扰源”加上一条“发射天线”的组合——板上的高频噪声(比如晶振的谐波)通过网口这个路径,以共模电流的形式耦合到网线上,而网线本身就是一根高效的 antenna,将噪声辐射出去。 简单来说,网口晶振(如:25MHz/5…时间:2025/11/13 -

; ) 电子设计中的EMI和EMC有什么区别?

(EMI & EMC CIRCUIT DESIGN THROUGH ISOLATION OF AD AND DC) What’s the Difference Between EMI and EMC in Electronic Designs? 电子设计中的EMI和EMC有什么区别? Ele…时间:2024/06/10

电子设计中的EMI和EMC有什么区别?

(EMI & EMC CIRCUIT DESIGN THROUGH ISOLATION OF AD AND DC) What’s the Difference Between EMI and EMC in Electronic Designs? 电子设计中的EMI和EMC有什么区别? Ele…时间:2024/06/10 -

; ) 展频晶振(Spread Spectrum)规格参数及使用说明

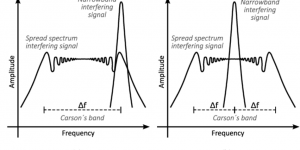

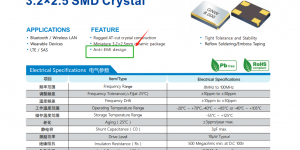

关于展频晶振(Spread Spectrum)的作用,晶诺威科技介绍如下: The Spread Spectrum Series are used in digital electronic systems to reduce the Electro-Magnetic Interference (E…时间:2024/05/14

展频晶振(Spread Spectrum)规格参数及使用说明

关于展频晶振(Spread Spectrum)的作用,晶诺威科技介绍如下: The Spread Spectrum Series are used in digital electronic systems to reduce the Electro-Magnetic Interference (E…时间:2024/05/14 -

; ) 晶振会产生电磁波干扰吗?

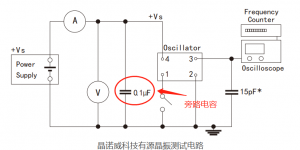

晶振会产生电磁波干扰吗? 答:会的。 晶诺威科技解释如下: 传统排除晶振电磁波干扰的方式:在回路中加入磁珠、滤波器、接地回路、以及金属屏蔽罩。作为晶振厂家,晶诺威科技也在优化晶振本身材质及电路设计,尽最大可能降低晶振对外界的干扰,同时,也增强了自身抗(来自外界的)干扰能力。 在有源晶振方面,则增加了…时间:2024/05/12

晶振会产生电磁波干扰吗?

晶振会产生电磁波干扰吗? 答:会的。 晶诺威科技解释如下: 传统排除晶振电磁波干扰的方式:在回路中加入磁珠、滤波器、接地回路、以及金属屏蔽罩。作为晶振厂家,晶诺威科技也在优化晶振本身材质及电路设计,尽最大可能降低晶振对外界的干扰,同时,也增强了自身抗(来自外界的)干扰能力。 在有源晶振方面,则增加了…时间:2024/05/12 -

; ) 关于晶振电磁兼容性(EMC)设计

关于晶振(晶体谐振器)在电路中的电磁兼容性(EMC)设计,晶诺威科技总结如下: For most digital applications, the crystal oscillator is a very critical frequency controlling component. It m…时间:2024/03/12

关于晶振电磁兼容性(EMC)设计

关于晶振(晶体谐振器)在电路中的电磁兼容性(EMC)设计,晶诺威科技总结如下: For most digital applications, the crystal oscillator is a very critical frequency controlling component. It m…时间:2024/03/12 -

; ) 关于展频晶振抗干扰与时钟精度的冲突问题

关于展频晶振抗干扰与时钟精度的冲突问题,晶诺威科技分析如下: Every electronic product designer has to deal with the issue of electromagnetic compatibility (EMC) or electromagnetic …时间:2024/01/19

关于展频晶振抗干扰与时钟精度的冲突问题

关于展频晶振抗干扰与时钟精度的冲突问题,晶诺威科技分析如下: Every electronic product designer has to deal with the issue of electromagnetic compatibility (EMC) or electromagnetic …时间:2024/01/19 -

; ) 关于多层PCB设计中晶振接地(GND)问题

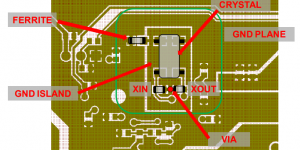

关于多层PCB设计中晶振接地(GND)问题,晶诺威科技解释如下: 在多层PCB设计中,合理的层叠设计有助于减小电磁干扰和信号干扰。通常,将信号层与地平面和电源平面隔开,有助于提高信号完整性和降低EMI。 地平面(Ground Plane) 指在电路设计中,用于连接和分布地(Ground)的导电区域。…时间:2024/01/17

关于多层PCB设计中晶振接地(GND)问题

关于多层PCB设计中晶振接地(GND)问题,晶诺威科技解释如下: 在多层PCB设计中,合理的层叠设计有助于减小电磁干扰和信号干扰。通常,将信号层与地平面和电源平面隔开,有助于提高信号完整性和降低EMI。 地平面(Ground Plane) 指在电路设计中,用于连接和分布地(Ground)的导电区域。…时间:2024/01/17 -

; ) 24MHz无源晶振EMC辐射超标问题分析与建议

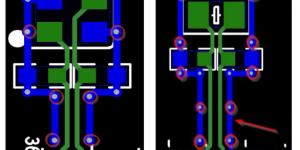

(4引线无源晶振与2引线无源晶振包地图示) 晶诺威科技关于24MHz无源晶振EMC辐射超标问题,分析与建议如下: 问题描述 某款触屏控制电路板,由于其外置无源贴片晶振SMD3225-4P 24MHz晶振布线不合理,导致EMC辐射超标。 原因分析 EMC三要素是干扰源,被干扰对象和干扰路径。而晶振作为…时间:2023/06/15

24MHz无源晶振EMC辐射超标问题分析与建议

(4引线无源晶振与2引线无源晶振包地图示) 晶诺威科技关于24MHz无源晶振EMC辐射超标问题,分析与建议如下: 问题描述 某款触屏控制电路板,由于其外置无源贴片晶振SMD3225-4P 24MHz晶振布线不合理,导致EMC辐射超标。 原因分析 EMC三要素是干扰源,被干扰对象和干扰路径。而晶振作为…时间:2023/06/15 -

; ) 关于晶体振荡器电路布线引发的问题(Layout Issues)

关于晶体振荡器电路布线引发的问题(Layout Issues),晶诺威科技解释如下: Good layout practices are fundamental to the correct operation and reliability of the oscillator. It is cri…时间:2023/06/06

关于晶体振荡器电路布线引发的问题(Layout Issues)

关于晶体振荡器电路布线引发的问题(Layout Issues),晶诺威科技解释如下: Good layout practices are fundamental to the correct operation and reliability of the oscillator. It is cri…时间:2023/06/06