有源晶振上升/下沿时间对系统的影响有哪些?

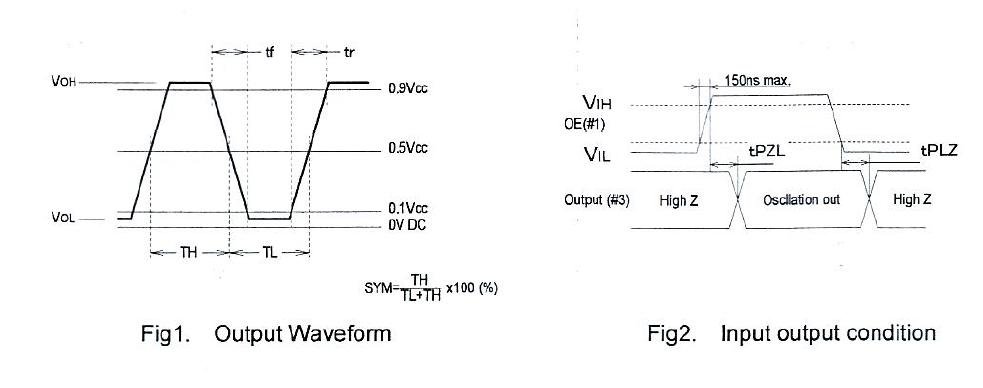

有源晶振的上升沿(tr)和下降沿(tf)时间(即信号从低电平到高电平或高电平到低电平的转换时间)对数字系统的性能和稳定性有重要影响。

关于有源晶振上升/下沿时间对系统的影响,晶诺威科技分析及归纳如下:

1、 信号完整性与噪声

过长的边沿时间:会导致信号在阈值电压附近停留时间过长,容易引入噪声或振铃(ringing),增加误触发的风险。可能引发信号反射(尤其在高速或长走线时),破坏信号完整性。

过短的边沿时间:虽然能减少时序模糊区,但会引入高频谐波,导致电磁干扰(EMI)问题,可能影响其他电路或通过辐射超标测试。

2、 时序精度与抖动(Jitter)

边沿时间越长,对电源噪声、地弹(ground bounce)等干扰更敏感,可能增加周期抖动(Period Jitter)或相位噪声(Phase Noise)。高速系统(如高频时钟、SerDes接口)对边沿时间敏感,过长的边沿会导致时序裕量(Timing Margin)减少。关键应用:例如,在高速ADC/DAC、FPGA或通信系统中,边沿时间不匹配可能导致采样误差或数据同步失败。

3、 功耗与热效应

更短的边沿时间通常意味着更高的开关电流(di/dt),导致动态功耗增加,可能引发电源噪声或局部发热。需权衡速度与功耗,尤其在低功耗设计中。

4、 系统兼容性

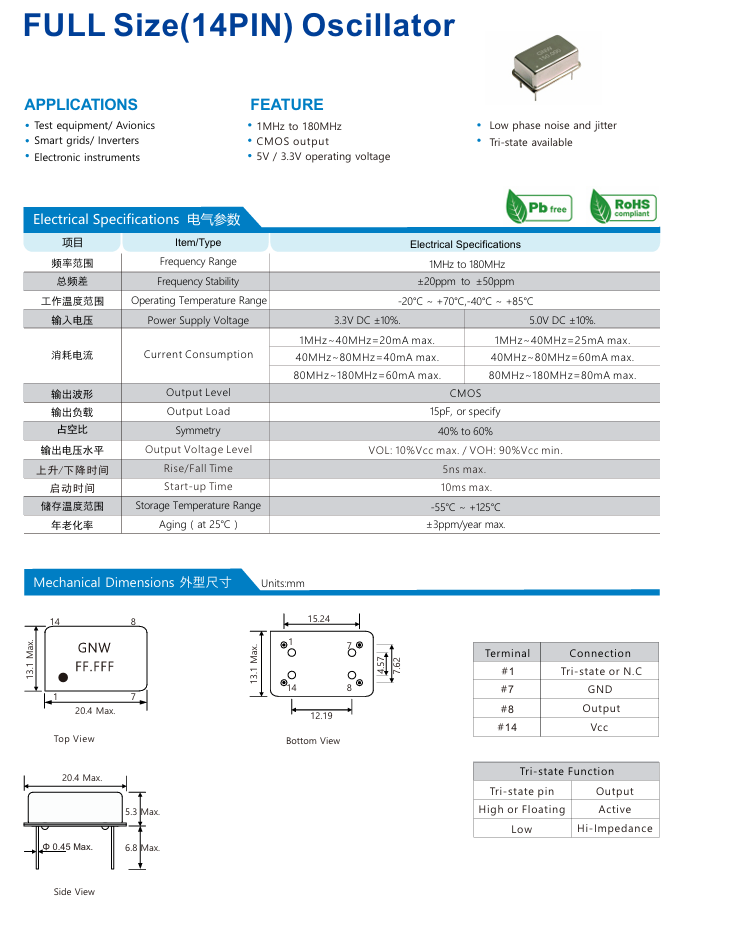

某些器件对输入时钟的边沿时间有明确要求(如某些MCU要求边沿时间<5ns)。不匹配可能导致逻辑错误。例如:过慢的边沿可能被 Schmitt Trigger 电路容错,但高速CMOS器件可能无法正确识别。

解决方案与设计建议

1、 选择合适的有源晶振:

根据系统速度需求选择边沿时间(通常数据手册会标注(Rise time/Fall time),如:<5ns)。

2、 PCB设计优化:

![]() 缩短时钟走线,避免分支,使用阻抗匹配(如端接电阻)以减少反射。

缩短时钟走线,避免分支,使用阻抗匹配(如端接电阻)以减少反射。

![]() 确保电源去耦,降低电源噪声影响。

确保电源去耦,降低电源噪声影响。

3、 信号调理:

若EMI严重,可适当增加串联电阻或尝试展频晶振。

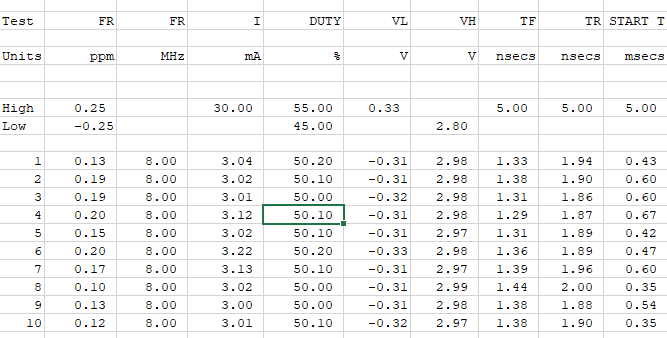

附:晶诺威科技测试数据范例

CMOS 8MHZ TCXO-DIP8 0.25PPM test data

TF: fall time 下降时间

TR: rise time 上升沿间