晶振负载电容大小有什么区别?

晶振的负载电容(Load Capacitance,通常表示为CL)是影响其工作频率稳定性和起振可靠性的关键参数。负载电容的大小选择不同,会带来以下区别:

1、 对频率稳定性的影响

负载电容过大:

会导致晶振的实际振荡频率偏低(电容增大,等效容抗降低,振荡回路时间常数增加);频率稳定性可能变差,尤其在温度变化或电压波动时。

负载电容过小:

会导致频率偏高,甚至可能引发泛音振荡(非基频振荡);可能因回路增益不足而难以起振,或输出波形失真。

2、 对起振可靠性的影响

匹配外部电容:

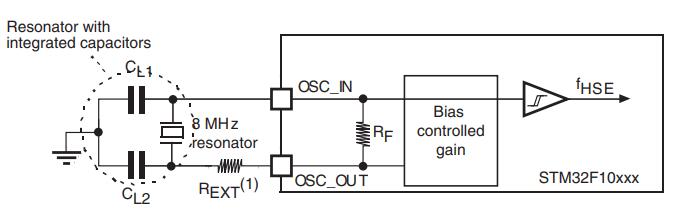

晶振的标称负载电容(如12pF、18pF、20pF等)需与外部匹配电容(通常为两个接地电容CL1、CL2)配合。若实际负载电容与标称值偏差过大,可能导致:

无法起振(回路无法满足相位和振幅条件);起振时间变长(如MCU因时钟未稳定而复位失败)。

注:电路中通常存在寄生电容,又名杂散电容(英文:Cstray),通常3~5pF,需要考虑进去。

3、 对功耗的影响

负载电容较大时:需要更大的驱动电流(因充放电时间延长),可能增加系统功耗;适用于对频率稳定性要求较高、功耗不敏感的场景。

负载电容较小时:功耗更低,但可能牺牲稳定性,适合低功耗设备(如电池供电设备)。

4、 与振荡电路的匹配

不同振荡模式:Pierce振荡电路(常见于MCU):

依赖负载电容提供180°相移,电容不匹配会导致频率偏移或停振。

CMOS振荡器:对负载电容敏感度较高,需严格匹配。

调整方法:

若实测频率偏差较大,可通过微调外部电容(如更换为可调电容)校准。