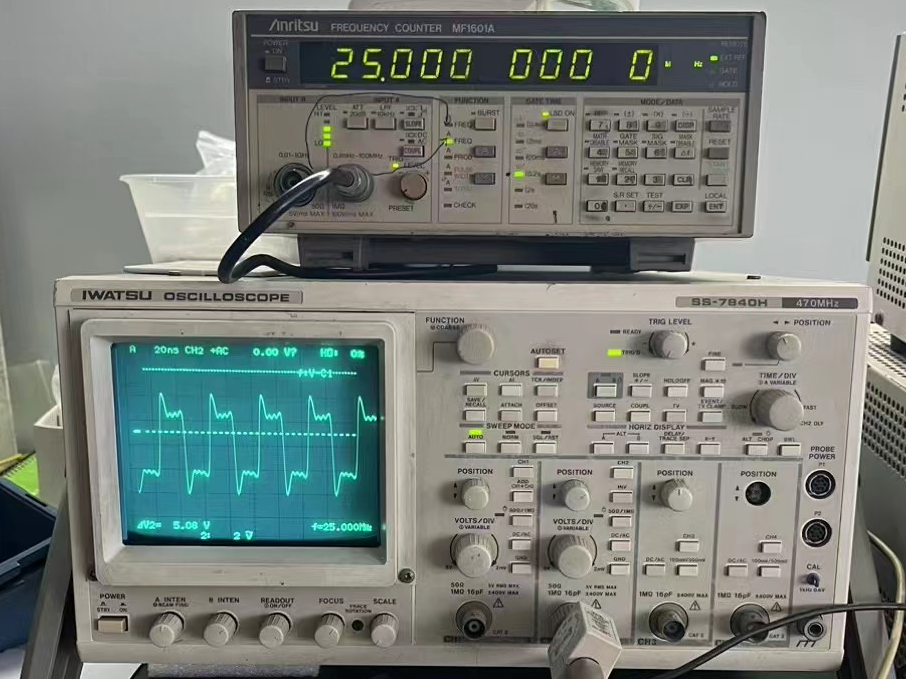

(25MHz晶振输出CMOS方波信号)

方波(CMOS)输出晶振可以代替削峰正弦波(Clipped Sinewave)输出晶振吗?

答:在确认目标芯片的时钟输入兼容方波,并且不担心EMI问题恶化的情况下,可以替换。否则请进行充分验证。

关于该问题。晶诺威科技分析及解释如下:

这大多数情况下可以,但需要仔细检查目标电路的输入要求和设计。

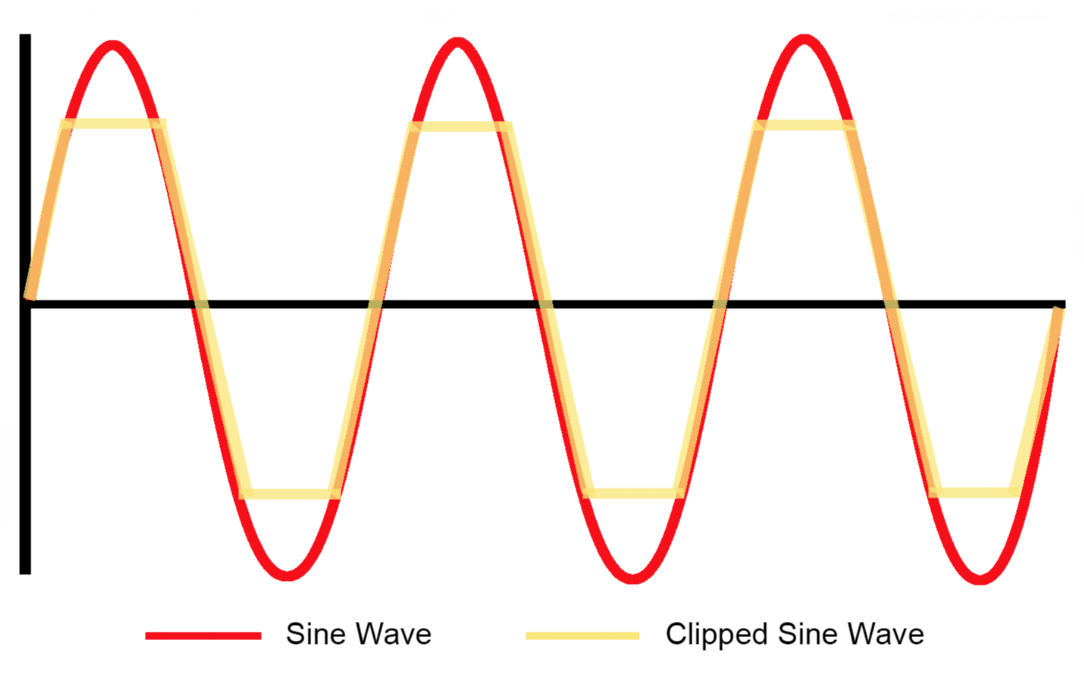

1、 削峰正弦波(Clipped Sinewave)

波形为一个被“削顶”的正弦波,使其更接近于方波,但仍然有圆滑的过渡。其特点是高频谐波成分比完美正弦波少,但比纯方波要多,输出电平通常用RMS或峰值电压来定义。其优势是对系统其他部分的电磁干扰相对较小。常见应用为一些对EMI敏感的射频电路、通信模块,或者其内部时钟电路设计为处理正弦波输入的芯片。

2、 方波(CMOS)

波形为理想的数字开关波形,具有快速上升和下降沿。其特点是包含非常丰富的高频奇次谐波。输出电平是标准的数字电平。其优势是驱动能力强,能与绝大多数数字电路直接兼容。常见应用包括微处理器、FPGA、内存、通用逻辑电路等几乎所有数字系统。

替换的考虑因素

在考虑用方波输出晶振代替削峰正弦波输出晶振时,必须评估以下几点:

1、 目标芯片的时钟输入要求(最关键!)

- 查看数据手册:找到你所用芯片的时钟输入引脚电气参数。

- 输入类型:它是否明确要求“正弦波”输入?有些高速ADC、射频芯片或特定微处理器可能要求正弦波时钟以减少抖动。

- 输入电平:削峰正弦波的电平(如0.5Vpp, 1Vpp)是否在目标芯片时钟输入的允许范围内?方波输出通常是固定的逻辑电平。

- 偏置电压:有些芯片的时钟输入内部有一个偏置电压,专门用于处理正弦波的中心点。如果直接接入方波,可能会导致工作点错误,甚至损坏输入级。这是一个常见的陷阱。

2、 电磁兼容性

方波输出由于其陡峭的边沿,会产生大量的高频噪声和谐波,可能导致:

- 系统内其他部分的EMI问题;

- 影响敏感的模拟电路或射频电路;

- 通过电源和地线串扰到其他部分。

如果原设计使用削峰正弦波,说明设计者可能已经考虑了EMI问题。直接替换为方波可能会使系统无法通过EMC测试,或在某些高灵敏度应用中引起性能下降。

3、 电源完整性

方波晶振在输出翻转的瞬间会产生较大的瞬态电流,对电源的“毛刺”更敏感,也可能给电源带来更多噪声。需要确保电源去耦设计良好。

如何进行替换评估和操作

1、 阅读主芯片数据手册:确认时钟输入是否兼容方波。绝大多数现代数字芯片都兼容。 阅读原晶振和新晶振的数据手册:对比输出电平、上升/下降时间、驱动能力等参数。

2、 在原有电路上,用高带宽示波器测量削峰正弦波时钟的波形、电压幅值。换上新的方波晶振后,再次测量波形,确保没有过冲、振铃,并且逻辑电平正确。

3、 系统测试

- 功能测试:替换后,系统是否能正常工作?

- 稳定性测试:长时间运行,特别是在高低温等极端情况下,系统是否稳定?

- EMI预测试:如果EMI对你很重要,需要进行相应的测试。

晶诺威科技建议:

1、对于绝大多数通用数字电路,如单片机、FPGA、CPLD等,用方波输出晶振直接替换削峰正弦波输出晶振通常没有问题,甚至是更好的选择,因为它提供了更清晰的边沿和更强的驱动能力。

2、对于射频、高速模拟、通信或对时序抖动要求极高的系统,需要极其谨慎。原设计使用削峰正弦波很可能是有意为之,为了降低相位噪声和EMI。在这种情况下,不建议随意替换。

3、最安全的方法:如果原设计指定了削峰正弦波,并且你不确定原因,最好遵循原设计。如果必须替换,请进行充分的分析和测试。