关于IC对无源晶振输出波形电压幅值要求的一些见解,归纳如下:

IC(集成电路)对无源晶振输出波形的电压幅值要求,通常由IC的输入电平规范决定。以下是关键要点和详细说明:

1、 典型电压幅值范围

CMOS电平:大多数现代IC(如MCU、数字芯片)要求晶振输出为满幅的CMOS电平,即:幅值接近电源电压(VDD),例如:

- 3.3V系统:幅值约 0.3V ~ 3.0V(峰峰值 ≈ 2.7V)

- 5V系统:幅值约 0.5V ~ 4.5V(峰峰值 ≈ 4.0V)

注意:实际幅值可能因晶振负载、电路损耗而略低,但需确保高于IC输入高电平(VIH)阈值。

2、 IC的具体要求

输入高电平(VIH):通常要求 > 0.7 × VDD(例如3.3V系统需 > 2.3V)。输入低电平(VIL):通常要求 < 0.3 × VDD。

晶振输出波形(一般为正弦波或削顶正弦波)的峰峰值需覆盖VIH和VIL范围,以确保可靠触发。

3、 影响因素

- 晶振参数:负载电容(CL)、等效串联电阻(ESR)会影响幅值。

- 匹配电路:IC内部通常集成反馈电阻(Rf)和增益放大器,外部需配合负载电容(CL1、CL2)设计。

- PCB布局:过长走线或干扰可能导致幅值衰减。

4、 测量与验证

- 使用高阻探头(≥10MΩ)测量,避免探头电容影响频率和幅值。

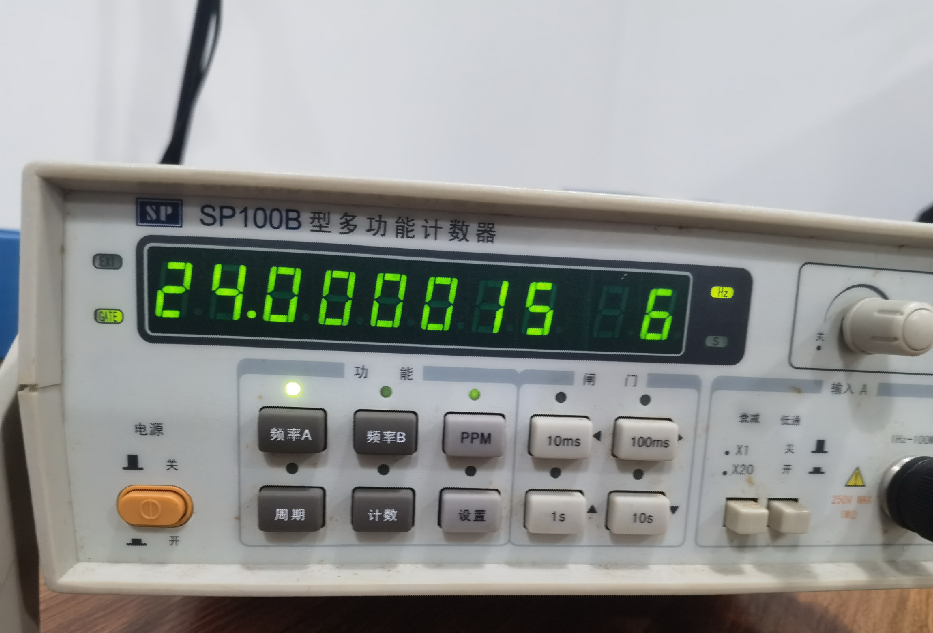

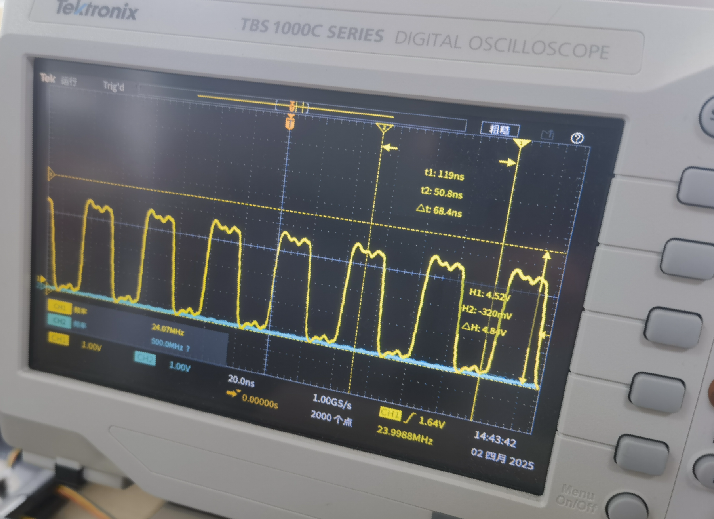

- 波形类型:无源晶振输出一般为正弦波,但经IC内部整形后变为方波供内部电路使用。24MHz无源晶振输出波形正弦波经由IC整形之后,如下图所示:

- 幅值不足的后果:可能导致时钟不稳定、启动失败或功耗增加。

5、 设计建议

参考IC数据手册:严格按推荐的晶振参数、负载电容值设计。

低功耗应用:需注意IC对晶振驱动强度的配置(如调整驱动电流)。

6、 常见问题

幅值过低:参考IC数据手册,严格按推荐的晶振负载电容参数。

幅值过高:可能导致过冲或EMI问题,可串联阻尼电阻(如22~100Ω)。