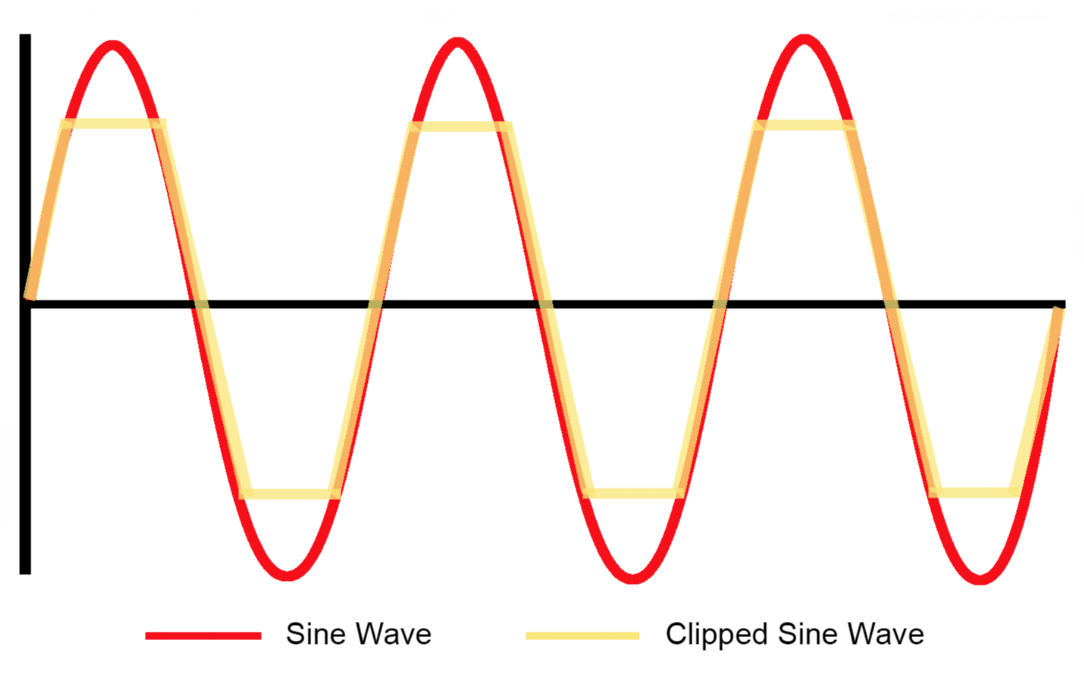

如何将TCXO Clipped Sine Wave(削峰正弦波)连接到时钟电路?

将削峰正弦波(Clipped Sine Wave)连接到时钟电路时,主要目的是将其转化为边沿陡峭的方波时钟信号。以下是连接方法和注意事项:

一、 为什么需要处理?

时钟电路通常需要边沿陡峭的方波信号(如CMOS/TTL电平),以确保可靠的时序和低抖动。削峰正弦波(Clipped Sine Wave)虽然近似方波,但其边沿可能不够陡峭,直接用作时钟可能导致时序误差、抖动或逻辑误触发。

CMOS 方波

二、推荐连接方案

方案A:使用施密特触发器(Schmitt Trigger)

作用:将缓慢变化的信号转化为边沿陡峭的方波,并抗噪声。

电路连接建议:

1、 将削峰正弦波输入到施密特触发器。

2、 选择适当的电源电压(如1.8、3.3V或5V)以满足目标时钟电路的逻辑电平。

3、 输出即为方波时钟信号。

优点:简单可靠,抑制噪声。

方案B:使用比较器(Comparator)

适用场景:需要精确调节阈值或高速场合。

电路连接建议:

1、 将削峰正弦波输入比较器。

2、 比较器的另一端接参考电压(如电源电压的一半)。

3、 输出通过上拉电阻连接到逻辑电源电压。

注意:高速比较器需注意PCB布局和电源去耦。

方案C:使用逻辑门(如反相器)

若削峰正弦波幅度已接近逻辑电平(如0V~5V),且边沿较陡,可直接通过逻辑门整形。

注意:需确保信号幅度不超过逻辑门的输入电压范围。

三、 关键参数检查

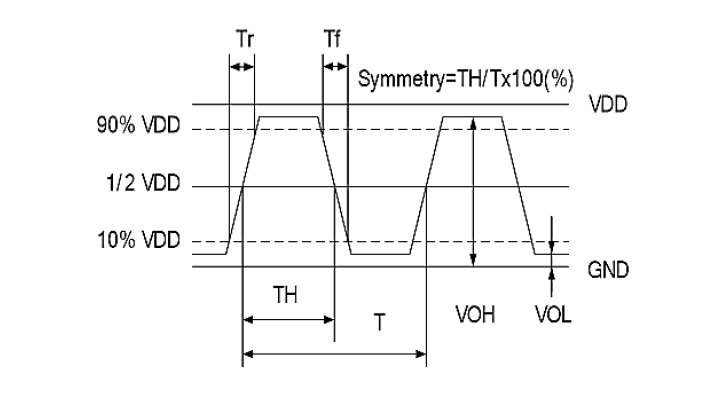

1、 电压匹配:

确保削峰正弦波的幅度符合时钟电路的输入要求(如CMOS:0.3VDD~0.7VDD)。若幅度不足,需先通过放大器或电平转换电路。

2、 频率范围:

所选整形电路(如施密特触发器)需支持目标频率(检查器件手册的“传输延迟”和“最大频率”)。

3、边沿要求:

若时钟电路对边沿斜率有严格要求(如高速ADC时钟),可能需要高速比较器。

4、 抗干扰与布局建议

- 去耦电容:在整形电路的电源引脚就近放置100nF电容;

- 阻抗匹配:若频率较高(>50MHz)或走线较长,需考虑端接匹配;

- 隔离:避免时钟线路靠近噪声源(如电源、模拟信号)。

四、测试验证,用示波器检查整形后的信号:

- 边沿是否足够陡峭(上升/下降时间);

- 有无过冲或振铃;

- 抖动是否在允许范围内。

以上内容仅供参考,TCXO Clipped Sine Wave(削峰正弦波)连接到时钟电路配置,请以实际应用为主。