CMOS(方波)输出有源晶振输出的电平不够怎么办?

CMOS输出的有源晶振,其输出电平在空载时应接近电源轨(VCC和GND)。如果电平不够,本质上只有两个原因:

1. 输出电流被“吃掉”了;

2. 输出能力被“限制”了。

排查步骤

操作:用电烙铁或热风枪,暂时断开晶振输出引脚与后续电路的连接(或者只焊上晶振,不焊连接电阻/负载)。

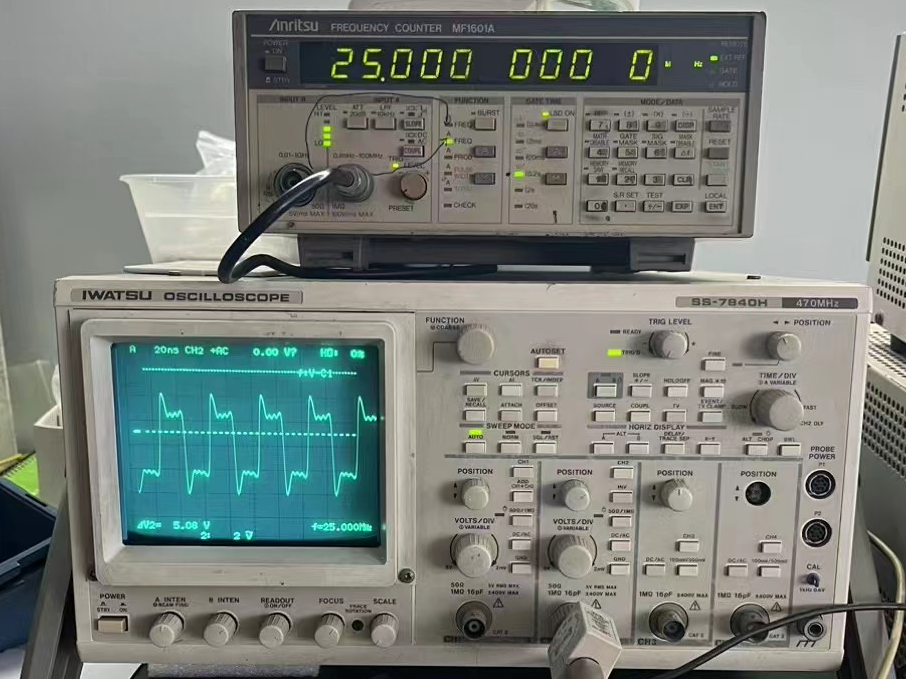

测量:用示波器 x10档探头 直接测量晶振的输出引脚。

判断:

如果此时波形完美(高电平近VCC,低电平近GND,上升/下降沿陡峭):100%确定是负载端的问题。进入负载问题排查。

如果此时波形依然不好:问题在晶振自身或电源。进入电源与晶振问题排查。

负载问题排查

现象:空载正常,接上负载后电平被拉低、波形边沿变缓。

建议

串联一个小电阻(Rs):在晶振输出和接收端之间串联一个22Ω ~ 100Ω的电阻。这是最简单有效的方案。它限制了瞬间充放电电流,改善了信号完整性,并减少了过冲和振铃,常常能使接收端测得的波形幅度更完整。

电源与晶振问题排查

现象:即使空载,输出电平也不达标。

查阅晶振数据手册,找到输出负载“Output Load ”这个参数。你电路中的实际总负载电容应小于这个标称值。如果你的电路CL=30pF,却选了一个CL=15pF的晶振,就可能驱动不足。

建议:

更换一个输出负载更大更大或驱动能力更强(有些厂家会标明“Strong Drive”)的有源晶振。

补充:晶振本身损坏或选型不当

1、晶振是否在额定频率和电压(1.8V、3.3V还是5V)下工作?

2、尝试更换一个同型号的新晶振,看问题是否解决。

3、检查输出使能(OE)引脚(如果有)是否为有效电平。

拓展阅读:晶振的Output Level(输出电平)

晶振的Output Level(输出电平),简单来说,就是晶振在正常工作时,输出引脚能产生的电信号的幅度或电压范围。

你可以把它理解为晶振输出信号的“音量”大小。它通常用以下两种方式描述:

波形与幅度:比如是削峰正弦波还是方波。方波的电平会接近其供电电压(如3.3V),而正弦波的幅度通常较低。

逻辑电平标准:常见的有LVCMOS(低压CMOS)、LVPECL(低压正发射极耦合逻辑)、LVDS(低压差分信号)等。它们各自有特定的电压摆幅(如LVDS的幅度约为350mV)。

这个参数的重要性在于兼容性。如果输出电平过低,后端芯片可能无法识别信号(导致无声或故障);如果过高,则可能损坏接收电路。同时,它也与功耗相关,通常电平越高、频率越快,功耗也越大。