系统深度休眠后被RTC唤醒后时间不准是什么原因?

这是MCU低功耗场景下的常见问题。晶诺威科技分析及总结原因如下:

1、 RTC时钟源问题

- LSI(内部低速RC)精度差:通常±2%~5%误差,受温度电压影响;

- LSE(外部32.768kHz晶振)不稳定:晶振起振慢,负载电容不匹配;

- 时钟分频配置错误

2、 深度睡眠下时钟行为

- 主时钟停止,仅RTC和备份域保持;

- RTC异步预分频器可能受唤醒过程影响;

- 备份域供电不稳定

3、 唤醒后系统时钟重配置

- 唤醒后主时钟重新初始化,可能干扰RTC计数

- 中断处理延迟导致时间累积误差

解决方案参考如下:

一、 硬件层面优化

1. 时钟源选择

- 优先使用外部LSE晶振(精度高)

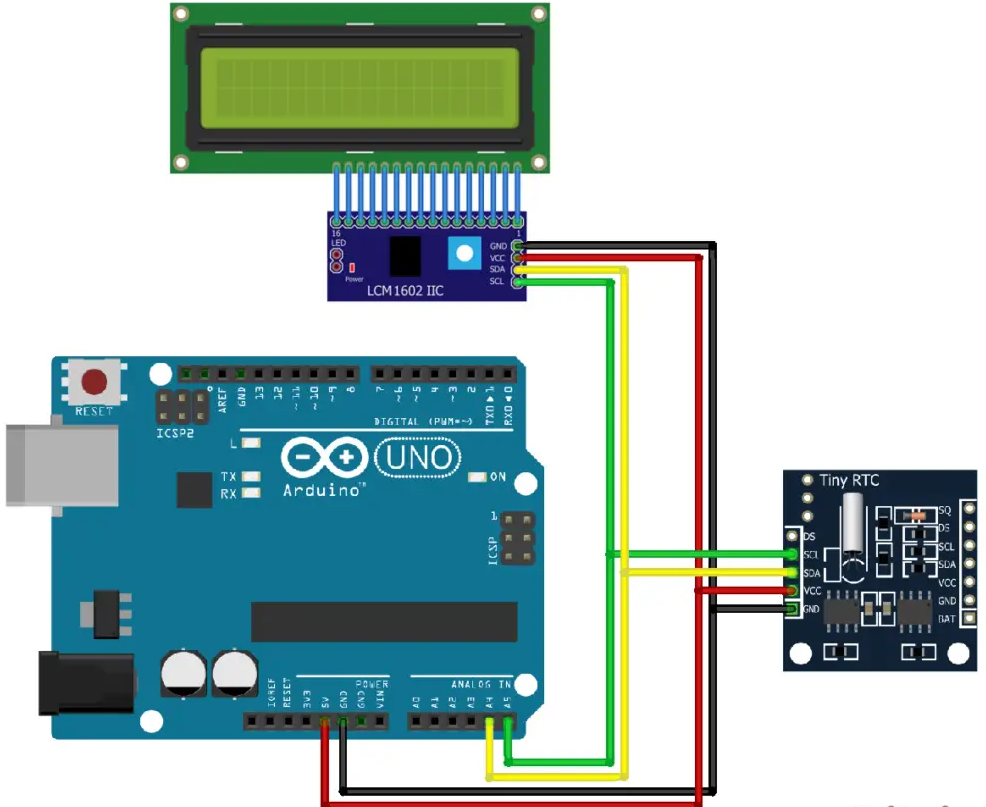

- 检查硬件:32.768kHz晶振 + 匹配电容

- 在RCC配置中启用LSE

2. 电源稳定性

- 确保Vbat引脚连接3V电池或电容(1-10μF)

- 深度睡眠前检查备份域电源状态

3. PCB布局优化

- 晶振靠近MCU,走线短

- 避免高频信号线靠近晶振

- 添加地屏蔽

二、 软件配置优化

1. RTC精确初始化

2. 深度睡眠与唤醒配置

3.软件校准补偿

三、 推荐配置方案

方案A:高精度要求(使用LSE)

- 硬件:外部32.768kHz晶振 + 10pF负载电容

- 软件:预分频器 127/255,启用RTC校准输出

- 校准:每周自动同步一次(如有网络)

方案B:低成本方案(使用LSI)

- 初始化时校准LSI

- 温度补偿(如果系统支持)

关键检查点

- Vbat引脚:必须连接(即使不使用电池,也要接1-10μF电容到地)

- 晶振负载电容:匹配晶振要求

- PCB布局:晶振走线≤10mm,远离干扰源

软件顺序:

- 先使能备份域访问

- 再配置RTC

- 深度睡眠前确保RTC配置完成

- 唤醒后:立即调用RTC_WaitForSynchro()