有源晶振LVCMOS是什么输出逻辑?

LVCMOS全称Low Voltage Complementary Metal-Oxide-Semiconductor,即低压互补金属氧化物半导体。它是一种广泛应用于现代数字集成电路(如微处理器、FPGA、存储器等)的输入/输出逻辑标准和电路结构。我们通常说“LVCMOS输出”时,指的是符合这种电气标准的数字信号。

LVCMOS是经典CMOS逻辑的低电压版本,其核心特点如下:

1. 电压水平低:

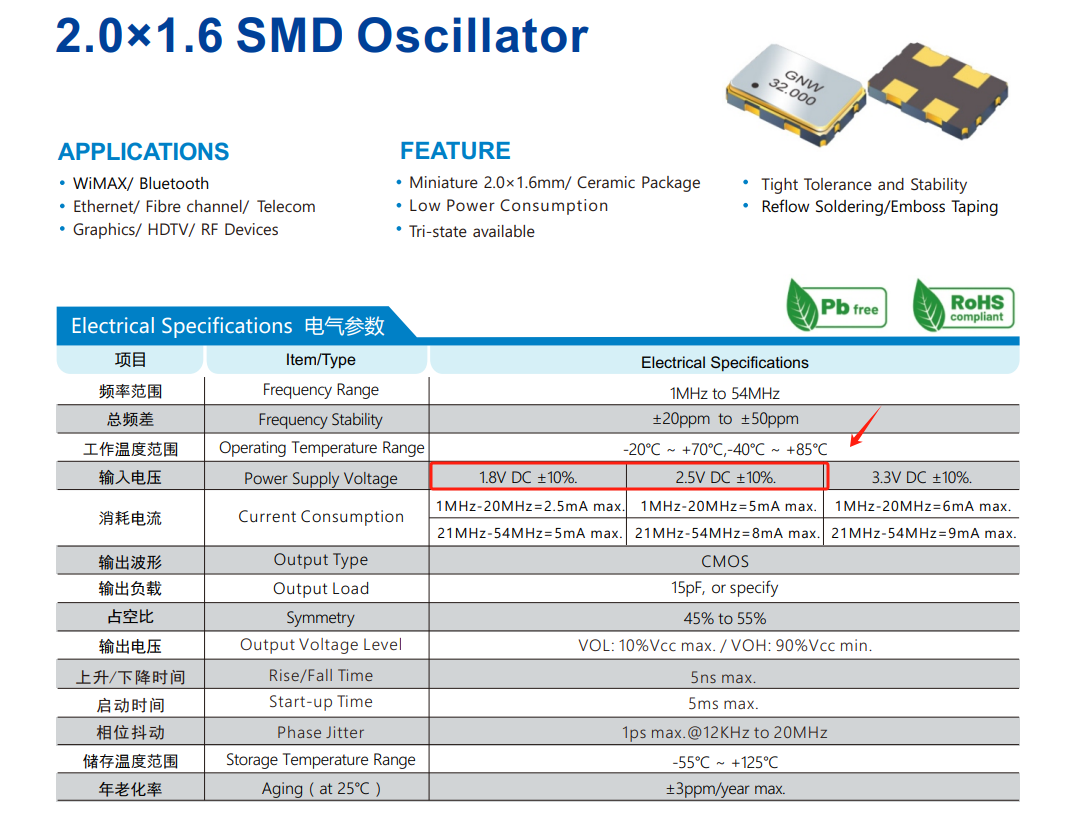

这是它与老式5VCMOS(如HC/HCT系列)最显著的区别。常见的LVCMOS电平包括:

- LVCMOS 3.3V:逻辑高电平VOH≈3.3V,逻辑低电平VOL≈0V。

- LVCMOS 2.5V:对应2.5V供电。

- LVCMOS 1.8V:对应1.8V供电。

- LVCMOS 1.2V:对应更先进的低功耗工艺。

降低电压的主要目的是降低功耗(动态功耗与电压的平方成正比)和适应更小的晶体管工艺。

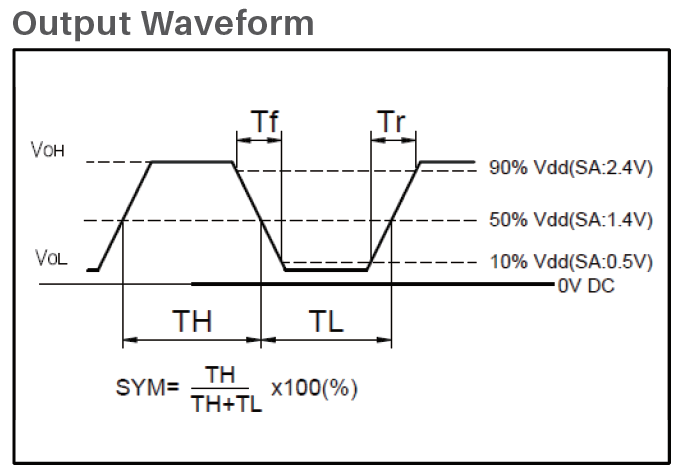

LVCMOS输出逻辑电平示例(以3.3V系统为例),通常用输入/输出电压的阈值来定义:

输出端:

保证的逻辑高电平最小值VOH_min:通常≥0.9×VDD≈2.97V。

保证的逻辑低电平最大值VOL_max:通常≤0.1×VDD≈0.33V。

实际输出在空载时通常非常接近理想的3.3V和0V。

输入端:

能识别为逻辑高电平的最小值VIH_min:通常≥0.65×VDD≈2.15V。

能识别为逻辑低电平的最大值VIL_max:通常≤0.35×VDD≈1.15V。

在VIL_max和VIH_min之间的区域是不确定区,逻辑状态未定义,应避免信号长时间处于此区域。

优点

1. 低静态功耗:稳定状态下,总有一个MOS管完全截止,从电源到地的直流路径被切断,理论上静态电流为零。

2. 高速:上升下降沿陡峭,开关速度快。

3. 高噪声容限:逻辑摆幅(高电平和低电平之差)较大,抗干扰能力较强。

4.驱动能力强:输出阻抗低,可以驱动多个负载或较长的走线(在速度要求不高时)。

LVCMOS输出逻辑是现代数字系统中最主流的单端数字信号输出方式。它本质上是基于特定低压电源的、采用推挽结构的CMOS数字电平。其核心特点是低电压、低静态功耗、强驱动能力和陡峭的边沿。在设计电路时,需要确保驱动LVCMOS输出的器件电源电压与接收端输入的电压标准兼容,并且在高速应用时关注其信号完整性问题。

补充说明:

LVTTL:早期3.3V系统常用,输入阈值是固定的(如1.5V),而LVCMOS阈值与VDD成比例。现代器件大多已融合或统称为3.3V CMOS。