晶振输出波形比较乱是什么原因?

答:晶振输出波形“乱”,通常指的是波形失真、有毛刺、幅度异常或频率不稳。这背后可能涉及电路匹配、PCB布局、外部干扰或器件本身等多个环节。

关于晶振输出波形比较乱问题,晶诺威科技分析如下:

一、核心电路匹配问题

负载电容不匹配:

如果实际电容与晶振规格书要求的负载电容(CL)偏差过大,波形很容易畸变。理想情况下,外接电容需要结合PCB的寄生电容(通常3-5pF)来计算,公式大致为 CL = (Cg*Cd)/(Cg+Cd) + 寄生电容。

驱动功率不当:

如果波形看起来像被削平了顶部,变成了近似方波,很可能是驱动功率过大,导致晶振过激励。反之,如果波形幅度很小,甚至起振困难,可能是驱动功率不足。

负性阻抗不足:

这是衡量振荡回路稳定性的指标,如果它小于晶振等效串联电阻(ESR)的5倍,电路就容易受外界影响而不稳定。

二、PCB布局与测量方法

PCB布局不合理:

晶振的走线过长、离高频干扰源太近,或者下方穿过信号线,都容易引入寄生电容和电磁干扰,破坏波形。

测量方法引入失真:

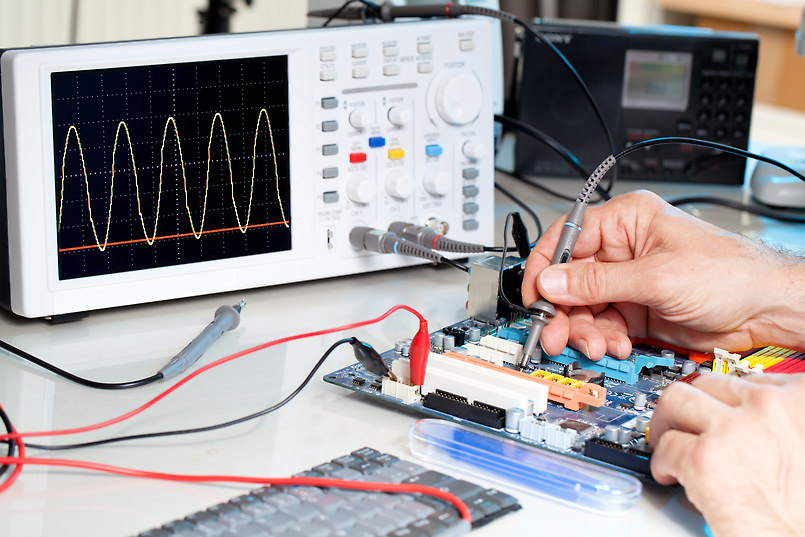

直接用高阻抗示波器探头(×10档)接触晶振引脚,可能会改变振荡条件,导致频率偏移甚至停振。建议使用有源探头,或在探头前端串联一个小电阻来减小影响。

三、外部环境干扰

电源噪声与电磁干扰:

不稳定的电源纹波(例如100mV的纹波)就可能给波形带来额外抖动。周围如果有强电磁场,也可能让波形出现毛刺。

温度变化:

温度变化会引起晶振频率漂移,如果温差大,频率不稳定也会让波形看起来“乱”。

建议:

1、 减少干扰:在电路设计时,应尽量远离强电磁场和高压线,同时采用屏蔽等措施减少外部干扰。

2、 电容匹配:选择适当的电容进行匹配,以保持负载的稳定性,避免负载变化对晶振输出频率的影响。

3、 择合适的晶振:根据实际应用环境选择具有适当温度系数的晶振,以减少温度变化对输出频率的影响。