关于TMS320C6713开发板25MHz有源晶振使用说明,晶诺威科技介绍如下:

针对TMS320C6713开发板使用25MHz有源晶振,核心的考量在于电平匹配、硬件连接方式以及芯片工作模式的配置。该型号有源晶振本身是一个完整的振荡器,输出的是稳定的CMOS方波,与无源晶振需要DSP内部振荡电路驱动不同,它直接为DSP提供时钟信号。

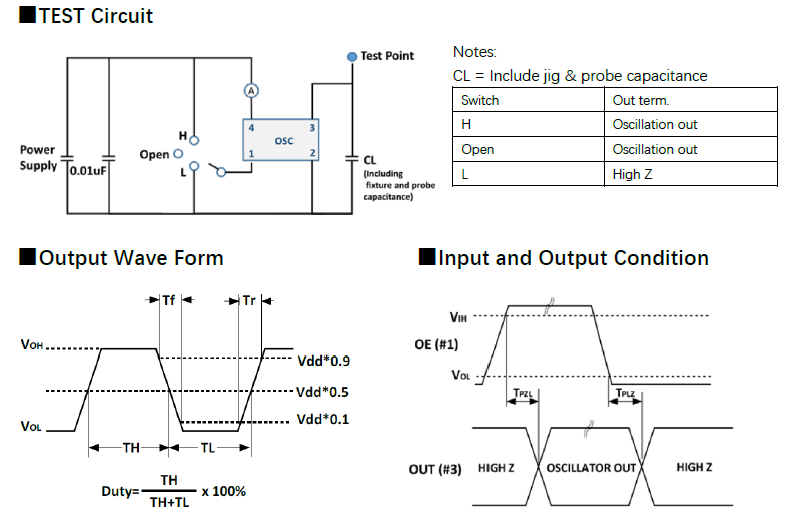

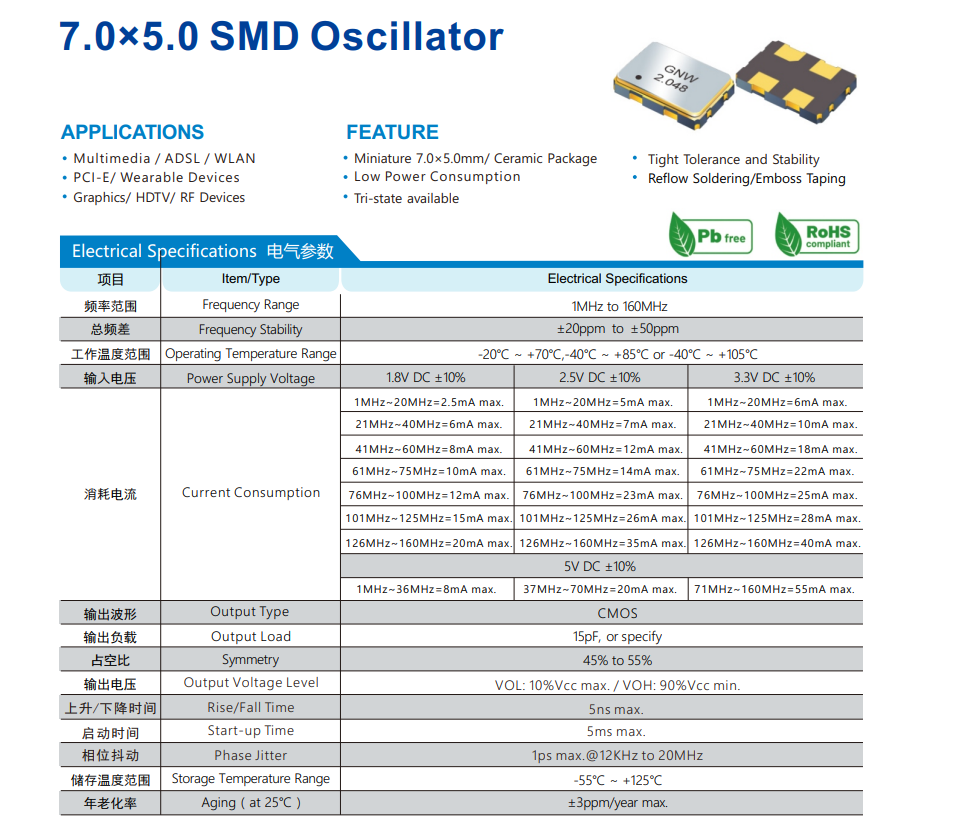

晶诺威科技产有源晶振OSC7050系列规格参数:

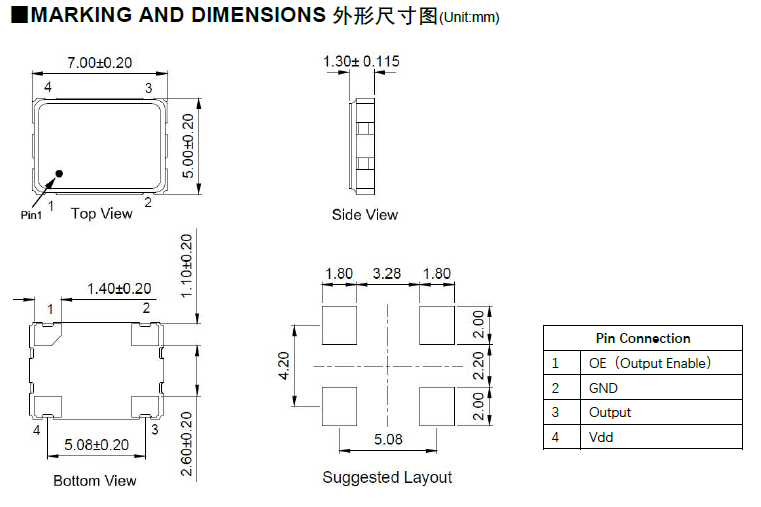

引脚连接:

![]() 输出端(OUT):直接连接到DSP的CLKIN引脚。这是时钟信号的输入引脚。

输出端(OUT):直接连接到DSP的CLKIN引脚。这是时钟信号的输入引脚。

![]() 使能端(OE,可选):部分有源晶振有一个使能引脚,用于控制输出。通常可以上拉(接VCC)使其始终使能,或连接到DSP的GPIO引脚,以便在软件中控制时钟的开启与关闭。

使能端(OE,可选):部分有源晶振有一个使能引脚,用于控制输出。通常可以上拉(接VCC)使其始终使能,或连接到DSP的GPIO引脚,以便在软件中控制时钟的开启与关闭。

![]() 电源(VCC):这是最关键的一步。必须为有源晶振提供稳定的3.3V电源。因为TMS320C6713的I/O电压是3.3V,直接使用3.3V供电的晶振,其输出电平与DSP的输入引脚兼容,无需额外进行电平转换。

电源(VCC):这是最关键的一步。必须为有源晶振提供稳定的3.3V电源。因为TMS320C6713的I/O电压是3.3V,直接使用3.3V供电的晶振,其输出电平与DSP的输入引脚兼容,无需额外进行电平转换。

![]() 接地(GND):连接至电路板的地。

接地(GND):连接至电路板的地。

模式配置:

硬件连接好后,需要通过配置DSP的CLKMODE0引脚来告诉芯片时钟源的类型。对于有源晶振,应将该引脚设置为0,选择外部振荡器模式。

软件配置:通过PLL倍频至系统时钟

提供25MHz的基准时钟后,DSP内部的PLL(锁相环)模块可以将这个频率倍频到更高的系统时钟。你可以通过配置PLL寄存器来获得所需的核心频率(最高300MHz)和外设时钟。

目标模块 相关配置 计算示例 (以25MHz输入,PLLx18为例)

DSP核心 (SYSCLK1) PLLDIV1 寄存器 450 MHz (25MHz × 18 / 1)

外设时钟 (SYSCLK2) PLLDIV2 寄存器 112.5 MHz (25MHz × 18 / 4)

EMIF时钟 (ECLKOUT) PLLDIV3 寄存器 90 MHz (25MHz × 18 / 5)

注意:

核心频率最终不能超过芯片的最大额定值,不同速度等级的C6713上限不同(如200MHz或300MHz)。配置PLL时,一个关键的步骤是必须先将其置于旁路(Bypass)模式,完成所有分频、倍频寄存器的配置,等待PLL稳定锁定后,再将时钟源切换回PLL输出。

使用有源晶振的优势与注意事项

有源晶振的信号质量更好,稳定性更高,抗干扰能力强。如果板子上没有焊接晶振的负载电容(或者不确定),或者需要更高精度的时钟源,用有源晶振会更省心。

故障排查:

如果上电后仿真器无法连接,或者程序无法运行,建议先用示波器测量一下DSP的CLKIN引脚。如果测不到预期的25MHz波形,问题很可能就出在晶振供电(3.3V)是否正确,或者CLKMODE0引脚的上拉/下拉电阻是否配置正确上。