关于有源晶振三态Tri-state,使能OE, E/D及待机ST的知识,晶诺威科技解释如下:

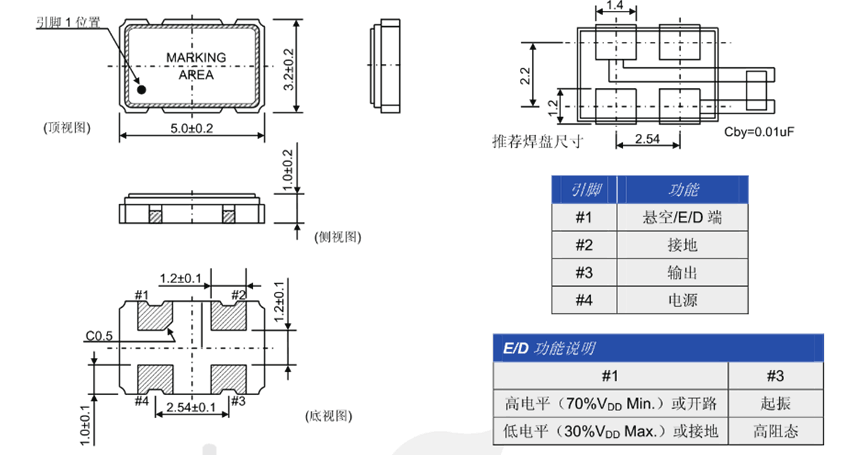

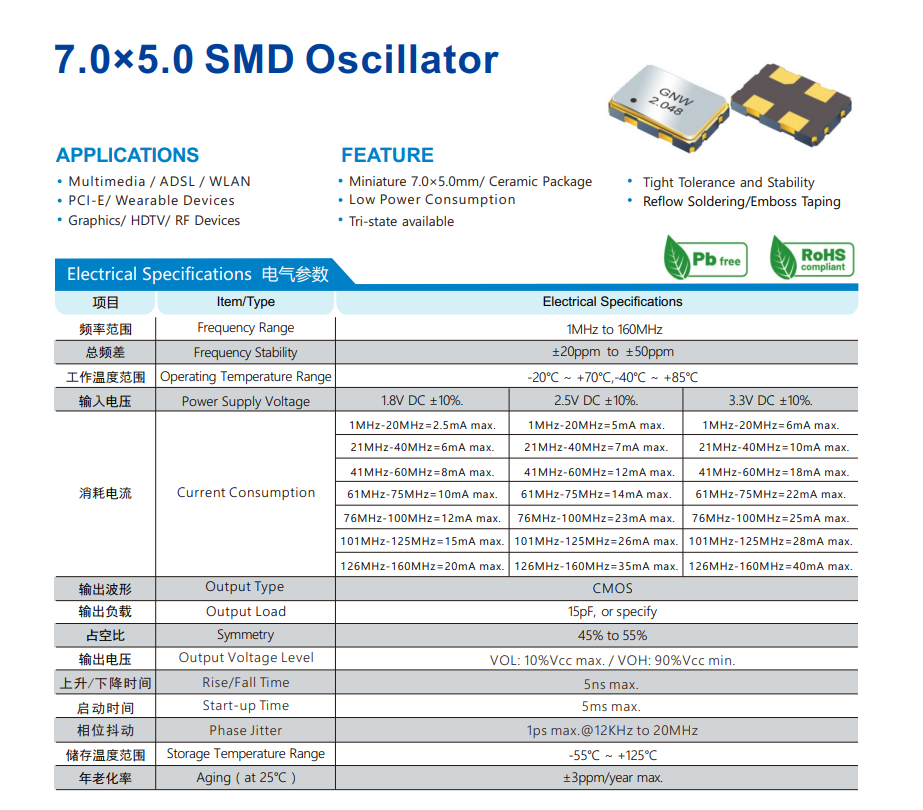

有源晶振(石英晶体振荡器)的脚1(又被称之为1号脚或pin#1)通常是Output Enable(OE)或者Enable/Disable (E/D)。也会叫做Stand-by (ST), Power Down (PD), 或者Inhibit (INH)。

使/能(E/D)

当引脚1被激活时,可以使1或者0,会导致输出时钟变为三态(Tri-state)或者高阻抗(Hi-Z)。三态功能允许输出引脚处于高阻抗状态,从而有效的从电路中移除振荡器的输出。

- 高逻辑电平(≥70%VDD):输入使能(Output Enable)

- 低逻辑电平(≤30%VDD):输出禁用(Output Disable)

如果选择OE功能,就等同于给有源晶振增加了一个“开关”功能。

待机功能Stand-by (ST)

在集成电路中STAND-BY脚指“待机模式”,即休眠,此时IC内部只有极微量的电流流过,需要解除待机模式后,IC才能正常工作。而晶振的STAND BY功能也是同样原理,IC待机时,晶振同样处于待机状态。IC启动,则晶振开始正常工作(启动时间为3~10ms),为IC正常工作提供频率信号,IC基于这些时序信号完成所有指令。若是以电池供电的便携式相关电子应用,待机模式(待机电流为10uA左右)会减少功耗,对电池寿命有好处。

由以上可见,若电子设备为直通电源供电(对功耗不敏感),且对开机速度有要求,建议直接取消晶振三态功能。

晶振三态功能取消方式:

把三态引脚(Tri-state)连接到VCC/VDD端或做“悬空”处理即可。