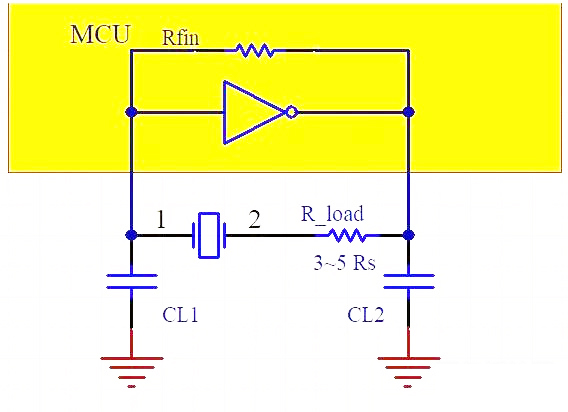

无源晶振起振电路设计:关于C0/C1, CL及RR说明如下:

C0/C1对晶体稳定性的影响

晶体(无源晶振)的静态电容C0和动态电容C1大小,与晶片电极面积大小(体积大小)成正比,不同厂家设计C0也有差异。

同一频率C0/C1的不同会影响振荡电路的稳定性:

C0/C1大,频率上升到标称频率前电抗变大,起振快,频率难调整,但不易受外面杂散电容影响,适合高稳需求;

C0/C1小,频率变量大,易受杂散电容影响,频率温度稳定性变差,但易于CL调整频率。

建议:

先求稳后求精准度,要合理控制C0/C1范围。

晶振负载CL对相噪和起振的影响

负载电容CL是电路中跨接晶体两端的总的有效电容,主要影响负载谐振频率和等效负载谐振电阻,与晶体一起决定振荡器电路的工作频率,通过调整负载电容,就可以将振荡器的工作频率微调到标称值。

CL大,远端相噪好;CL过大,难调整到标称频率,还容易导致回路阻抗增大,难起振;CL小,容易调整频率,近端相噪好,易起振。

晶振阻抗RR对振幅和激励功率的影响

同频率晶体的体积越小RR越大,RL晶体加负载电容的谐振阻抗, RL=RR(1+C0/CL)² 。根据其大小,评估振荡电路设计振荡宽限,满足振荡电路的振幅条件和激励功率等级。

P=I²*RL,可根据电流I的大小评估激励功率等级和匹配相应的限流电阻。

I:晶体谐振时流经晶振的电流,与RR成反比

RL:等效电阻

P:实际跨在晶体上的功率。