外接电容选择不当会对晶振电路造成什么影响?

如果晶振的外接电容值选择不当,可能会对电路产生以下影响:

1、频率稳定性:电容值过小可能导致频率稳定性下降,容易受到外界因素的干扰。电容值过大可能会使频率偏离标称值。

2、起振问题:电容值不合适可能导致晶振无法正常起振或起振困难。

3、功耗增加:不恰当的电容值可能会增加电路的功耗。

4、噪声干扰、错误的电容值可能会引入额外的噪声或干扰,影响电路的性能。

为了确保晶振的正常工作和电路的稳定性,建议根据晶振的规格书和实际需求选择合适的外接电容值。通常,晶振生产厂家会提供推荐的电容值范围。在选择电容时,还需要考虑电容的质量、温度特性和稳定性等因素。

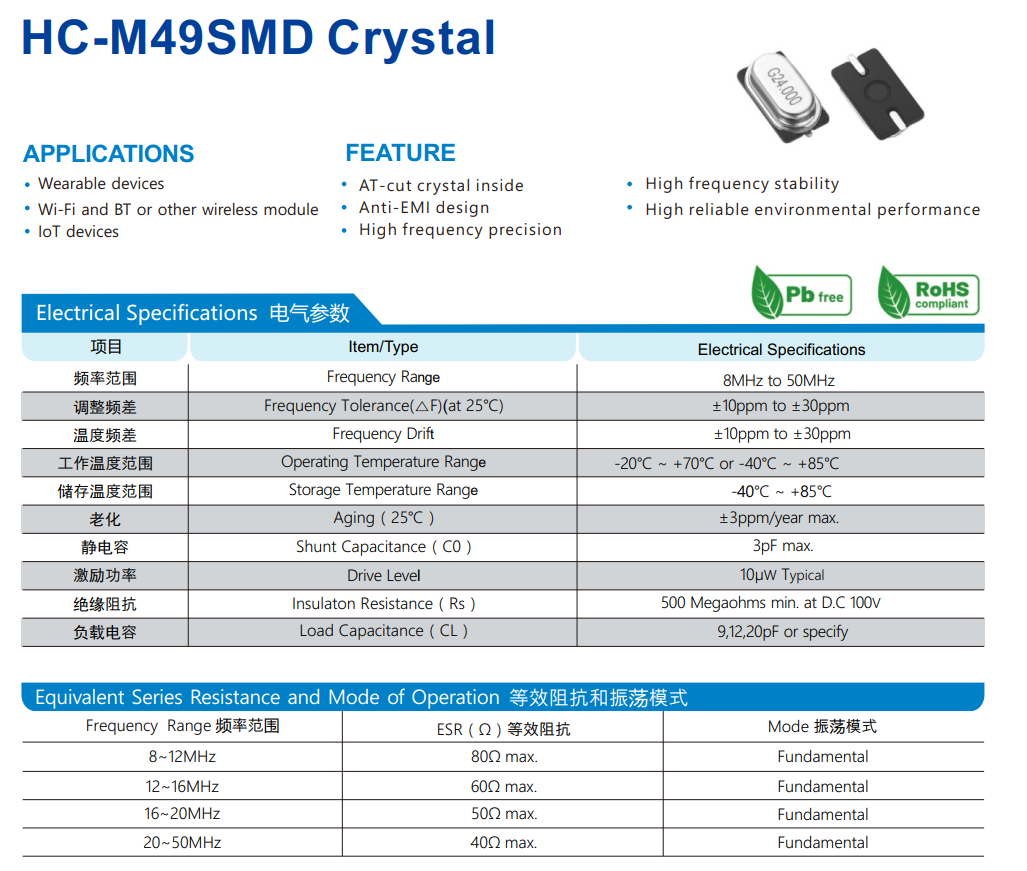

举例:晶诺威科技产HC-M49SMD晶振常见负载电容(CL):9pF、12pF或20pF。其规格参数详情如下:

拓展阅读:晶振电容应靠近晶振引脚还是MCU引脚放置?

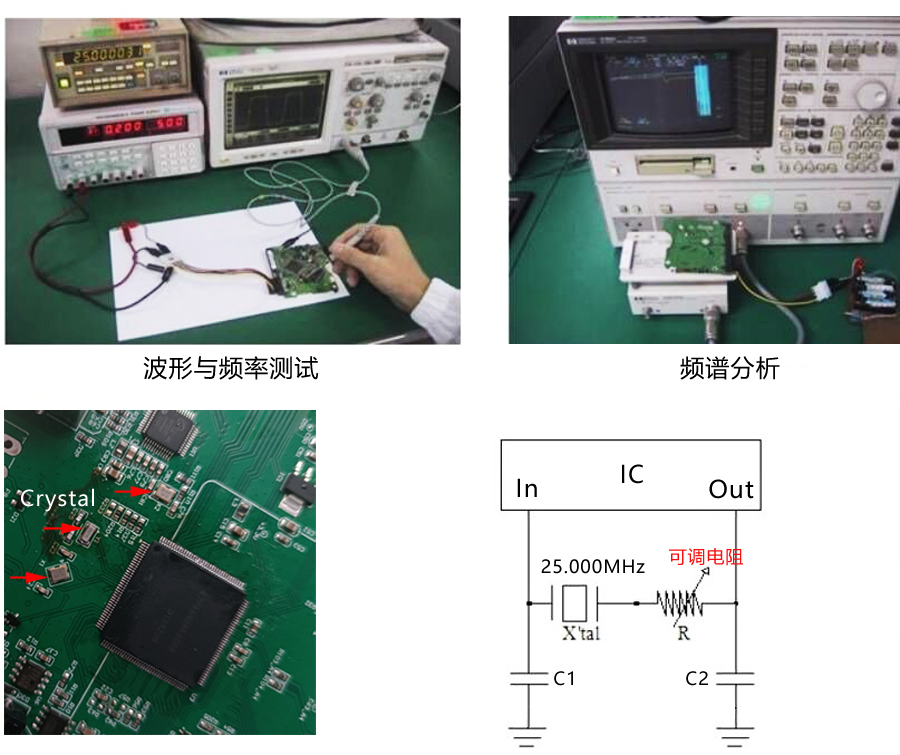

这是PCB布局中高频易被忽视却影响起振可靠性的关键问题。实践中常见错误是将两个负载电容(如22pF)对称布设在晶振与MCU之间,或刻意靠近MCU引脚以“缩短到芯片的距离”。但根据EMI抑制原理和寄生参数建模,电容必须紧邻晶振两端(即并联在XTAL/XTAL1引脚之间),且走线越短、越粗、越对称越好。

原因:

晶振为高阻抗谐振器件,其等效串联电阻(ESR)极小,任何引线电感(>0.5nH/mm)都会与电容形成额外LC谐振,导致相位裕度下降、起振延迟甚至停振;而MCU端引脚内部已集成反相放大器及缓冲结构,对电容位置不敏感。实测表明,电容距晶振>3mm时,-40℃低温起振失败率可升高5~10倍。

正确做法:

电容焊盘直接打孔紧贴晶振焊盘,禁用过孔换层,且避开电源/数字走线干扰区。