-

; ) 无源晶振(晶体谐振器)两个外接电容不一样可以吗?

无源晶振(晶体谐振器)两个外接电容不一样可以吗? 答:在绝大多数情况下,不建议将晶振的两个外接电容设计成不一样的,最好使用相同容值的电容。 虽然在某些特定条件下,使用不等值电容是一种调试技巧,但这属于非常规操作,需要谨慎对待。 关于外接电容选择问题,晶诺威科技详解如下: 一、使用相等电…时间:2026/04/05

无源晶振(晶体谐振器)两个外接电容不一样可以吗?

无源晶振(晶体谐振器)两个外接电容不一样可以吗? 答:在绝大多数情况下,不建议将晶振的两个外接电容设计成不一样的,最好使用相同容值的电容。 虽然在某些特定条件下,使用不等值电容是一种调试技巧,但这属于非常规操作,需要谨慎对待。 关于外接电容选择问题,晶诺威科技详解如下: 一、使用相等电…时间:2026/04/05 -

; ) 为何相同频率的晶振,负载电容pF值却不一样?

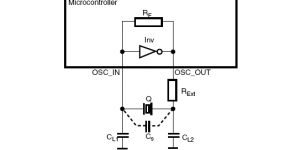

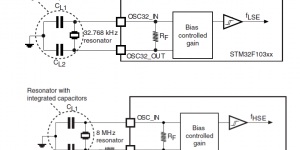

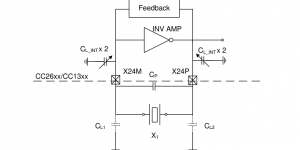

无源晶振皮尔斯振荡电路 为何相同频率的晶振,负载电容PF值却不一样? 答:“相同频率的晶振,其标称负载电容(Load Capacitance, CL)值可以不同”是完全正常且常见的现象。这并不意味着晶振有问题,而是反映了不同的设计选择和匹配要求。 负载电容(CL)是晶振外部需要连接的两个电容(CL1…时间:2026/03/03

为何相同频率的晶振,负载电容pF值却不一样?

无源晶振皮尔斯振荡电路 为何相同频率的晶振,负载电容PF值却不一样? 答:“相同频率的晶振,其标称负载电容(Load Capacitance, CL)值可以不同”是完全正常且常见的现象。这并不意味着晶振有问题,而是反映了不同的设计选择和匹配要求。 负载电容(CL)是晶振外部需要连接的两个电容(CL1…时间:2026/03/03 -

; ) 无源晶振(Crystal Resonator)内部有电容吗?

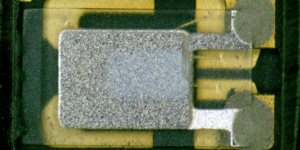

贴片式无源晶振(Crystal Resonator)内部解剖图 无源晶振(Crystal Resonator)内部有电容吗? 答:无源晶振(Crystal Resonator)内部没有电容。 晶诺威科技详解如下: 1、 无源晶振的本质 无源晶振的核心是一块经过精密切割并镀上电极的石英晶体片。它利用的…时间:2025/09/11

无源晶振(Crystal Resonator)内部有电容吗?

贴片式无源晶振(Crystal Resonator)内部解剖图 无源晶振(Crystal Resonator)内部有电容吗? 答:无源晶振(Crystal Resonator)内部没有电容。 晶诺威科技详解如下: 1、 无源晶振的本质 无源晶振的核心是一块经过精密切割并镀上电极的石英晶体片。它利用的…时间:2025/09/11 -

; ) 外部晶振的频率误差受匹配电容和电阻的影响吗?

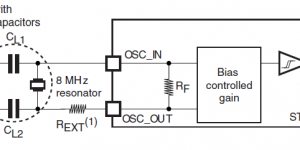

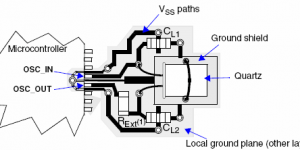

外部晶振的频率误差受匹配电容和电阻的影响吗? 答:会的。若电容和电阻不匹配,可能造成外部晶振输出频率误差过大,严重时导致其起振困难或直接停振。 如下图(以最常见的皮尔斯振荡电路)为例: CL1和CL2为匹配电容,又叫外接电容;Rext为匹配电阻,又叫串联电阻。时间:2025/06/07

外部晶振的频率误差受匹配电容和电阻的影响吗?

外部晶振的频率误差受匹配电容和电阻的影响吗? 答:会的。若电容和电阻不匹配,可能造成外部晶振输出频率误差过大,严重时导致其起振困难或直接停振。 如下图(以最常见的皮尔斯振荡电路)为例: CL1和CL2为匹配电容,又叫外接电容;Rext为匹配电阻,又叫串联电阻。时间:2025/06/07 -

; ) 晶振用不合适的电容会怎样?

晶振用不合适的电容会怎样? 答:如果所选匹配电容不合适,可能会造成晶振频偏超差、起振慢或不起振等问题。 建议通过IC手册获取争取的晶振负载电容或咨询晶振供应商。时间:2024/12/14

晶振用不合适的电容会怎样?

晶振用不合适的电容会怎样? 答:如果所选匹配电容不合适,可能会造成晶振频偏超差、起振慢或不起振等问题。 建议通过IC手册获取争取的晶振负载电容或咨询晶振供应商。时间:2024/12/14 -

; ) 关于STM32最小系统8MHz晶振电路的解释

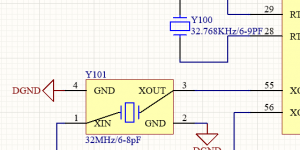

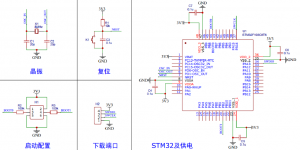

关于STM32最小系统8MHz晶振电路,晶诺威科技解释如下: 在STM32最小系统板上,8MHz晶振是用于提供系统时钟的外部晶体振荡电路之一。具体计算方法如下: 晶振频率=8MHz 晶振周期=1/晶振频率=0.125us 如果需要一个1秒的周期,需要多少个晶振周期? 1s/0.125us=80000…时间:2024/10/27

关于STM32最小系统8MHz晶振电路的解释

关于STM32最小系统8MHz晶振电路,晶诺威科技解释如下: 在STM32最小系统板上,8MHz晶振是用于提供系统时钟的外部晶体振荡电路之一。具体计算方法如下: 晶振频率=8MHz 晶振周期=1/晶振频率=0.125us 如果需要一个1秒的周期,需要多少个晶振周期? 1s/0.125us=80000…时间:2024/10/27 -

; ) 芯片对晶振外接匹配电容的配置要求

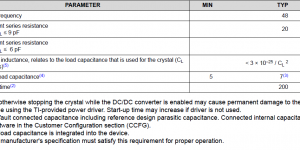

(该芯片推荐晶振负载电容为:最小值5pF,典型值7pF,最大值9pF) 关于芯片对晶振外接匹配电容的配置要求,需要仔细阅读芯片手册相关内容。 举例:某款芯片对晶振外接电容配置说明如下: On-chip default connected capacitance including reference…时间:2024/09/09

芯片对晶振外接匹配电容的配置要求

(该芯片推荐晶振负载电容为:最小值5pF,典型值7pF,最大值9pF) 关于芯片对晶振外接匹配电容的配置要求,需要仔细阅读芯片手册相关内容。 举例:某款芯片对晶振外接电容配置说明如下: On-chip default connected capacitance including reference…时间:2024/09/09 -

; ) NPO/NP0和C0G是同一种电容吗?

NPO/NP0和C0G是同一种电容吗? 答:NPO/NP0和C0G是同一种电容。 一般情况下,大家习惯把NPO写成NP0(零)。NPO是“Negative-Positive-Zero” 的简写,用来表示其温度特性。“O”或“0”在这里的意思一样,均表示电容温度特性好,不会随温度变化而出现容值漂移。 …时间:2024/08/29

NPO/NP0和C0G是同一种电容吗?

NPO/NP0和C0G是同一种电容吗? 答:NPO/NP0和C0G是同一种电容。 一般情况下,大家习惯把NPO写成NP0(零)。NPO是“Negative-Positive-Zero” 的简写,用来表示其温度特性。“O”或“0”在这里的意思一样,均表示电容温度特性好,不会随温度变化而出现容值漂移。 …时间:2024/08/29 -

; ) 关于外接电容COG(NPO)贴片电容选型注意事项

(无源晶振电路中的外接匹配电容CL1和CL2) COG(NPO)贴片电容简述 COG(NPO)贴片电容属于Class 1温度补偿型电容。它的容量稳定,几乎不随温度、电压、时间的变化而变化。尤其适用于高频电子电路。 COG(NPO)贴片电容特性 具有最高的电容量稳定性,在-55℃~125℃工作温度范围…时间:2024/08/18

关于外接电容COG(NPO)贴片电容选型注意事项

(无源晶振电路中的外接匹配电容CL1和CL2) COG(NPO)贴片电容简述 COG(NPO)贴片电容属于Class 1温度补偿型电容。它的容量稳定,几乎不随温度、电压、时间的变化而变化。尤其适用于高频电子电路。 COG(NPO)贴片电容特性 具有最高的电容量稳定性,在-55℃~125℃工作温度范围…时间:2024/08/18 -

; ) 关于无源晶振电路中外接电容CL1和CL2的选取

关于无源晶振电路中外接电容CL1和CL2的选取,晶诺威科技解释如下: 英文解释: For CL1 and CL2,it is recommended to use high quality ceramic dielectric capacitance (typically) between 5pF …时间:2024/06/02

关于无源晶振电路中外接电容CL1和CL2的选取

关于无源晶振电路中外接电容CL1和CL2的选取,晶诺威科技解释如下: 英文解释: For CL1 and CL2,it is recommended to use high quality ceramic dielectric capacitance (typically) between 5pF …时间:2024/06/02