无源晶振(晶体谐振器)两个外接电容不一样可以吗?

答:在绝大多数情况下,不建议将晶振的两个外接电容设计成不一样的,最好使用相同容值的电容。 虽然在某些特定条件下,使用不等值电容是一种调试技巧,但这属于非常规操作,需要谨慎对待。

关于外接电容选择问题,晶诺威科技详解如下:

一、使用相等电容 (常规做法)

绝大多数通用电路,也是芯片数据手册推荐的标准设计。

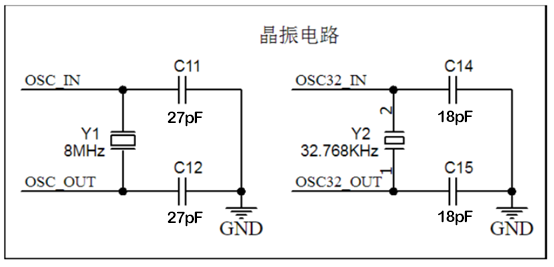

(外接电容C3=C4=18PF)

特点及优势:

稳定可靠:保证了振荡电路的平衡,是晶振正常工作的基础 。

计算简便:方便计算和匹配晶振的负载电容,从而获得精准的频率 。

二、使用不等电容 (非常规技巧)

加快起振:一大一小两个电容可以破坏电路的平衡点,帮助晶振更快地启动 。

调整反馈:减小输入端的对地电容,可以增大正反馈量,有助于解决起振困难的问题。

缺点与风险:

频率不准:破坏了电路的平衡,可能导致振荡频率偏离标称值,引起时钟偏差 。

稳定性差:可能导致输出波形畸变,甚至在温度变化或电压波动时发生停振 。

特定调试场景:

仅在电路存在起振困难,且设计者明确知道自己在做什么的情况下,作为一种调试手段临时使用。

为什么常规设计要使用相等电容?

这要从晶振的工作原理说起。在单片机电路里,晶振和两个电容共同构成一个“电容三点式振荡器”。这两个电容在这里扮演着两个关键角色:

决定频率:晶振对负载电容(CL)有明确要求(比如20pF)。这个负载电容的值,主要由两个外接电容(C1, C2)和电路板上的寄生电容(Cs)共同决定。它们的关系是 CL = (C1*C2)/(C1+C2) + Cs 。只有当 C1 = C2 时,计算和匹配才是最简便、最准确的。一旦两者不等,实际加载到晶振上的电容就会偏离设计要求,导致频率不准 。

维持平衡:这两个电容还决定了电路的反馈系数。当它们相等时,反馈系数为0.5,这是一个设计上公认的、能够稳定工作的平衡点 。如果两者相差太大,这种平衡就会被打破,轻则输出波形失真,重则导致电路停振 。

为了保证电路的稳定和精准,请遵循以下原则:

首选相等:除非有特殊调试需求,否则务必选择两个容值相同的电容。这也是绝大多数芯片参考设计和成熟产品中的标准做法 。

精准计算:电容值不是随便选的,需要根据晶振规格书中的负载电容(CL) 和电路板的寄生电容(Cs) 通过公式计算出来。对于新手,一个安全的选择是直接参考MCU或芯片数据手册中推荐的电容值 。

对称布局:在画电路板(PCB)时,让晶振到两个电容、再到芯片引脚的走线尽可能短且对称,这样可以减少寄生电容的引入和干扰 。

拓展阅读:晶振电容应靠近晶振引脚还是MCU引脚放置?

这是PCB布局中高频易被忽视却影响起振可靠性的关键问题。实践中常见错误是将两个负载电容(如22pF)对称布设在晶振与MCU之间,或刻意靠近MCU引脚以“缩短到芯片的距离”。但根据EMI抑制原理和寄生参数建模,电容必须紧邻晶振两端(即并联在XTAL/XTAL1引脚之间),且走线越短、越粗、越对称越好。

原因:

晶振为高阻抗谐振器件,其等效串联电阻(ESR)极小,任何引线电感(>0.5nH/mm)都会与电容形成额外LC谐振,导致相位裕度下降、起振延迟甚至停振;而MCU端引脚内部已集成反相放大器及缓冲结构,对电容位置不敏感。实测表明,电容距晶振>3mm时,-40℃低温起振失败率可升高5~10倍。

正确做法:

电容焊盘直接打孔紧贴晶振焊盘,禁用过孔换层,且避开电源/数字走线干扰区。