关于高精度晶振和高稳定性晶振的差异,晶诺威科技解释如下:

1、 高精度晶振

定义:初始频率与标称频率的偏差极小。

特点:

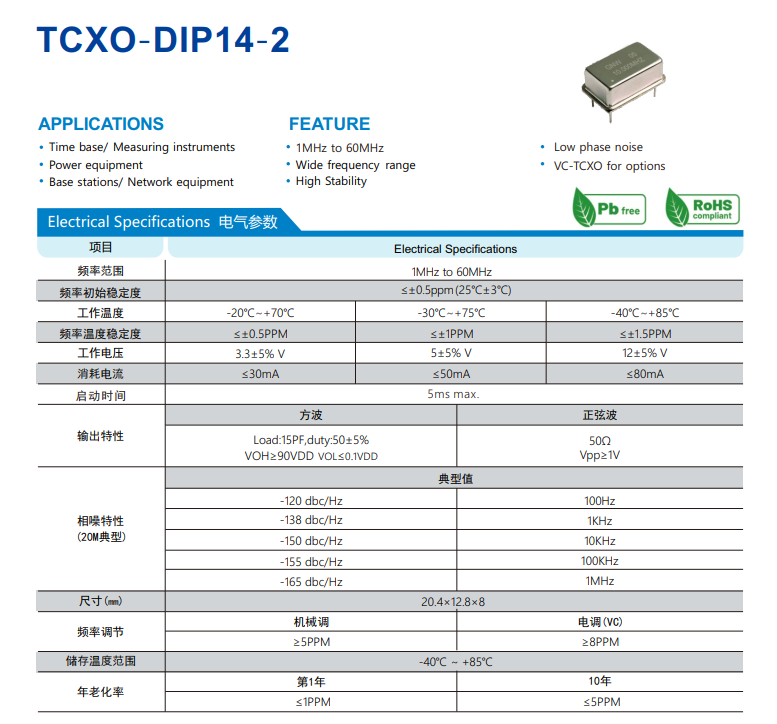

初始精度高:出厂时频率误差非常小,通常在±1 ppm(百万分之一)以内。

应用场景:

适用于对初始频率要求极高的领域,如通信基站、精密仪器等。

2、 高稳定性晶振

定义:在温度变化、时间推移等条件下,频率保持稳定。

特点:

温度稳定性好:在宽温度范围内频率变化小,通常用±0.1 ppm/°C表示。

长期稳定性好:随时间推移频率变化小,通常用±1 ppm/年表示。

应用场景:

适用于环境变化大或长期运行的系统,如卫星、军工设备等。

拓展阅读:关于晶振频率准确度和频率稳定度的区分

频率准确度

频率准确度是指晶振的实际输出频率与其标称频率之间的偏差。通常用ppm(百万分之一)来表示,数值越小,表示晶振的实际频率越接近理想值。例如,一个标称为12MHz的晶振,如果其频率准确度为10ppm,那么它的实际频率偏差就是120Hz。

频率准确度受到多种因素的影响,包括制造公差、初始调节误差、温度变化以及电源电压变化等。即使是同一批次的晶振,也可能因为细微的加工误差而表现出不同的频率准确度。

此外,出厂校准时可能存在的微小误差也会影响频率准确度。温度变化对频率准确度的影响尤为显著,尽管在+25℃室温下晶振的准确度较高,但温度的变化会导致频率的偏移。电源电压的波动同样会导致频率的偏移,因此在实际应用中需要特别注意供电电压的稳定性。

频率稳定度

频率稳定度描述的是晶振的频率随时间、温度、电源电压、机械振动等因素变化的程度。它衡量的是在不同环境条件下,晶振频率的漂移情况。

与频率准确度相比,频率稳定度更多地关注的是晶振在长期使用过程中的频率变化情况。

温度是影响频率稳定度的主要因素之一。不同晶振的温度漂移特性各不相同,因此需要在选择晶振时特别关注其温度特性。电源电压的波动同样会影响晶振的频率稳定度,因此稳定的供电对于保持晶振的频率稳定至关重要。此外,晶振的频率还会随时间逐渐变化,这种变化通常以ppm/年来表示,称为晶振的老化。机械振动和冲击也可能导致晶振频率的瞬时漂移,因此在设计电路时需要采取必要的隔离和抗震措施。

选型建议

晶振选型时,需要根据具体的应用需求来权衡频率准确度和频率稳定度。

对于要求精确计时或高精度通信的应用,如通信基站、卫星导航系统等,需要选择频率准确度和频率稳定度都较高的晶振。

对于一些对精度要求相对较低的消费类电子产品,如普通的智能家电,可以适当放宽对频率准确度和频率稳定度的要求。

在使用晶振时,为了确保其频率稳定性,可以采取一系列措施。例如,选择合适的晶振类型,避免晶振直接暴露在较大的温度变化下,采用温度补偿方法来实时监测温度变化并对频率进行补偿控制,保持供电电压的稳定性,以及采取隔离措施来减少机械振动和电磁干扰的影响。

频率准确度和频率稳定度是衡量晶振性能的重要指标。在选购和使用晶振时,需要充分了解这两个概念并根据具体的应用需求来选择合适的晶振类型和采取相应的措施来保持其频率稳定性。通过优化选材、控制温度、稳定供电和隔离外部干扰等措施,可以提高晶振的频率稳定性,从而确保电子设备和系统的正常、稳定、精确运行。

拓展阅读:关于晶振上升/下降时间与占空比对信号质量的影响

晶振频率正确也可能导致系统采样错误、通信异常或启动不稳定,这通常与信号边沿速度和占空比有关。

时钟信号不仅控制系统节拍,还定义每一拍的时序边界。在微控制器(MCU)、现场可编程逻辑器件(FPGA)、以及串行器/解串器(SerDes)等高速器件中,信号边沿的微小偏差或抖动会影响采样精度。

在FPGA系统中,如果时钟上升沿过慢,不同逻辑通道间的采样触发点可能出现微秒级偏差,导致时序裕量被压缩;若占空比偏离50%,触发信号提前或滞后,也会增加抖动与误码风险。

当上升/下降时间过慢或波形不对称时,时钟边界模糊,设备容易出现采样偏差。

一、参数含义

上升时间Tr:信号从低电平的10%Vdd上升到高电平90%Vdd所需的时间。下降时间Tr:信号从高电平的90%Vdd下降到低电平10%Vdd所需的时间。占空比Duty Cycle:一个周期内,高电平持续时间占总周期的比例,理想值为50%。

二、影响晶振波形质量的主要因素

不同输出类型的晶振适用于不同场景:差分输出晶振(LVDS、HCSL、LVPECL):边沿快、幅度低、抗干扰强,适合高速数字接口或高同步精度系统。CMOS/TTL输出:性能稳定,适合控制类电路或通用逻辑系统。射频/GPS系统:常用Clipped Sine或纯Sine输出,保证模拟信号完整性。

1、输出驱动结构

CMOS输出采用推挽电路,性能受晶振驱动能力和输出端负载影响,负载过大或驱动不足会减慢边沿速度。LVDS/HCSL采用恒流差分驱动,信号变化快、对称性好,抗干扰能力强。

2、负载电容和PCB走线

晶振内部有典型负载电容(如15pF),保证波形稳定。实际电路中,PCB 走线、电路输入端和其他器件的电容会与晶振内部电容一起形成总负载:总负载过大:上升/下降沿变慢;总负载过小:波形尖锐但易振铃或抖动。

3、电源噪声

晶振对电源纹波敏感,电源噪声会导致输出抖动。设计时应加滤波电容,保持地平面连续,让高速信号有稳定返回路径,减少反射和干扰。

4、设计建议

总负载尽量接近规格书推荐值,可通过PCB走线长度、控制阻抗、匹配电容实现;时钟走线短,阻抗约50Ω;差分线等长,保证同时到达,减少干扰和失真;走线远离高速信号和噪声源,必要时增加地隔离线。

在高性能应用的设计中,应该特别关注晶振的关键性能指标,如上升/下降时间(Rise/Fall Time)、占空比(Duty Cycle)等,以确保输出信号符合目标器件的接口要求。