-

; ) 有源晶振脚位功能说明

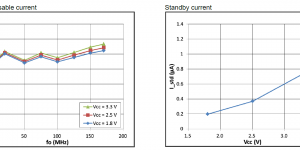

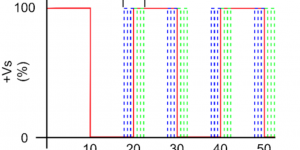

(Output disable current vs Standby current) 晶诺威科技有源晶振脚位功能说明如下: 1、 OE使能功能 High(高)or Open(悬空): Specified frequency output from OUT pin. 从OUT引脚输出指定频率 Low…时间:2022/11/18

有源晶振脚位功能说明

(Output disable current vs Standby current) 晶诺威科技有源晶振脚位功能说明如下: 1、 OE使能功能 High(高)or Open(悬空): Specified frequency output from OUT pin. 从OUT引脚输出指定频率 Low…时间:2022/11/18 -

; ) 抖动jitter的分类

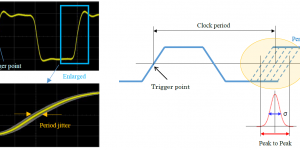

抖动jitter的分类 Depending on how the jitter timing is defined, jitter is classified into phase jitter, period jitter, and intercyclic jitter. Phase jitter…时间:2022/11/17

抖动jitter的分类

抖动jitter的分类 Depending on how the jitter timing is defined, jitter is classified into phase jitter, period jitter, and intercyclic jitter. Phase jitter…时间:2022/11/17 -

; ) How to obtain favorable phase noise? 如何获得良好的相位噪声?

How to obtain favorable phase noise? 如何获得良好的相位噪声? 1. Secure a favorable Q value of the oscillation circuit. Use a crystal with a high Q value, and low…时间:2022/11/16

How to obtain favorable phase noise? 如何获得良好的相位噪声?

How to obtain favorable phase noise? 如何获得良好的相位噪声? 1. Secure a favorable Q value of the oscillation circuit. Use a crystal with a high Q value, and low…时间:2022/11/16 -

; ) 无源晶振的第1脚和第3脚的接法

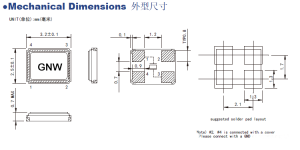

(4脚无源晶振SMD3225尺寸及脚位说明) 一般情况下,4脚无源晶振的第1脚和第3脚的接法如下: 无源晶振的第1脚和第3脚其实没有方向性,不用担忧接反。 具体操作: 若脚1接OSC-IN(频率输入),则脚3接OSC-OUT(频率输出) 若脚3接OSC-OUT(频率输出),则脚1接OSC-IN(频率…时间:2022/11/14

无源晶振的第1脚和第3脚的接法

(4脚无源晶振SMD3225尺寸及脚位说明) 一般情况下,4脚无源晶振的第1脚和第3脚的接法如下: 无源晶振的第1脚和第3脚其实没有方向性,不用担忧接反。 具体操作: 若脚1接OSC-IN(频率输入),则脚3接OSC-OUT(频率输出) 若脚3接OSC-OUT(频率输出),则脚1接OSC-IN(频率…时间:2022/11/14 -

; ) 谨防错误使用电烙铁破坏晶振

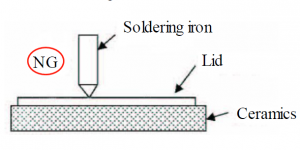

晶振会被电烙铁烫坏吗? 答:是的!超温且操作时间过长,晶振就会被电烙铁烫坏。 (电烙铁错误操作方式) 晶诺威科技解释如下: Please do not touch by hot soldering iron and do not put shock on top lid. 请不要通过高温烙铁顶住晶振…时间:2022/11/10

谨防错误使用电烙铁破坏晶振

晶振会被电烙铁烫坏吗? 答:是的!超温且操作时间过长,晶振就会被电烙铁烫坏。 (电烙铁错误操作方式) 晶诺威科技解释如下: Please do not touch by hot soldering iron and do not put shock on top lid. 请不要通过高温烙铁顶住晶振…时间:2022/11/10 -

; ) 晶振频差Frequency Tolerance 和晶振频偏Frequency Deviation

关于晶振频差Frequency Tolerance 和晶振频偏Frequency Deviation,解释如下: 晶振频差(英文:Frequency Tolerance) 在晶振数据手册中,“频差”指的是晶振的调整频差,具体指晶振频率与晶振本身中心频率的差值。在实际电路应用中,晶振被设计为可以处于该…时间:2022/11/09

晶振频差Frequency Tolerance 和晶振频偏Frequency Deviation

关于晶振频差Frequency Tolerance 和晶振频偏Frequency Deviation,解释如下: 晶振频差(英文:Frequency Tolerance) 在晶振数据手册中,“频差”指的是晶振的调整频差,具体指晶振频率与晶振本身中心频率的差值。在实际电路应用中,晶振被设计为可以处于该…时间:2022/11/09 -

; ) 关于MC-146内部晶振金属壳裸露问题的声明

关于MC-146内部晶振金属壳裸露问题的声明如下: The metal case inside of the molding compound may be exposed on the top or bottom of this product. This purely cosmetic and …时间:2022/11/08

关于MC-146内部晶振金属壳裸露问题的声明

关于MC-146内部晶振金属壳裸露问题的声明如下: The metal case inside of the molding compound may be exposed on the top or bottom of this product. This purely cosmetic and …时间:2022/11/08 -

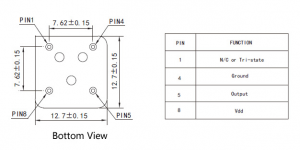

; ) 关于有源晶振脚位N/C与Tri-state的注解

有源晶振脚位PIN1:N/C与Tri-state功能说明 N/C If the product does not have the Tri-state function, no matter how Pin1 is connected, the product will work properly.…时间:2022/11/08

关于有源晶振脚位N/C与Tri-state的注解

有源晶振脚位PIN1:N/C与Tri-state功能说明 N/C If the product does not have the Tri-state function, no matter how Pin1 is connected, the product will work properly.…时间:2022/11/08 -

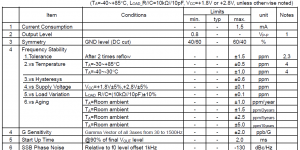

; ) TCXO温补晶振三种输出类型:削峰正弦波、正弦波或方波

TCXO温补晶振三种输出类型:削峰正弦波、正弦波或方波,说明如下: 1、Clipped Sine Wave:削顶(峰)正弦波 与方波相比,Clipped Sine Wave谐波分量少很多,但驱动能力较弱,通常为SMD3225、SMD2520、SMD2016等封装的表贴温补晶振使用的输出波形。例如: …时间:2022/11/03

TCXO温补晶振三种输出类型:削峰正弦波、正弦波或方波

TCXO温补晶振三种输出类型:削峰正弦波、正弦波或方波,说明如下: 1、Clipped Sine Wave:削顶(峰)正弦波 与方波相比,Clipped Sine Wave谐波分量少很多,但驱动能力较弱,通常为SMD3225、SMD2520、SMD2016等封装的表贴温补晶振使用的输出波形。例如: …时间:2022/11/03 -

; ) 为何不建议音叉KHz晶振过超声波?

(音叉晶振FC-135/SMD3215 32.768KHz) 为何不建议音叉KHz晶振过超声波?原因有二: 1、Tuning fork products oscillate at frequency bands that are close to the washing frequency of u…时间:2022/11/02

为何不建议音叉KHz晶振过超声波?

(音叉晶振FC-135/SMD3215 32.768KHz) 为何不建议音叉KHz晶振过超声波?原因有二: 1、Tuning fork products oscillate at frequency bands that are close to the washing frequency of u…时间:2022/11/02