-

; ) 方波晶振波形异常的解决方法

方波晶振波形异常现象: 方波晶振波形异常通常表现为过冲/振铃、波形圆钝/三角波或幅度不足,根源多在于测量方法不当、负载匹配错误或电路布局问题。 晶诺威科技建议: 先查探头设置和接地,再查匹配电阻和负载,大多数波形异常问题都能在这两步内解决。 可以按以下步骤逐一排查,通常能解决绝大多数异常: 1、排查…时间:2026/04/29

方波晶振波形异常的解决方法

方波晶振波形异常现象: 方波晶振波形异常通常表现为过冲/振铃、波形圆钝/三角波或幅度不足,根源多在于测量方法不当、负载匹配错误或电路布局问题。 晶诺威科技建议: 先查探头设置和接地,再查匹配电阻和负载,大多数波形异常问题都能在这两步内解决。 可以按以下步骤逐一排查,通常能解决绝大多数异常: 1、排查…时间:2026/04/29 -

; ) 无源晶振起振与芯片有关吗?

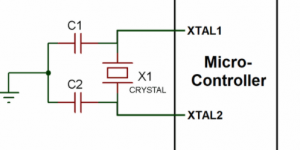

无源晶振起振与芯片有关吗? 答:是的,无源晶振能否成功起振,与芯片(通常是MCU、DSP、FPGA或SoC)有着非常密切且直接的关系。 无源晶振只是“谐振器”,芯片才是“驱动器”。两者必须电气特性匹配(频率、负载电容、等效串联电阻符合芯片要求),并且芯片的硬件连接和软件配置正确,才能成功起振。换句话…时间:2026/04/27

无源晶振起振与芯片有关吗?

无源晶振起振与芯片有关吗? 答:是的,无源晶振能否成功起振,与芯片(通常是MCU、DSP、FPGA或SoC)有着非常密切且直接的关系。 无源晶振只是“谐振器”,芯片才是“驱动器”。两者必须电气特性匹配(频率、负载电容、等效串联电阻符合芯片要求),并且芯片的硬件连接和软件配置正确,才能成功起振。换句话…时间:2026/04/27 -

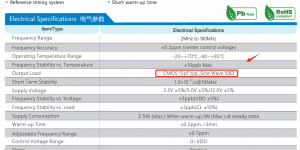

; ) TMS320C6713开发板25MHz有源晶振使用说明

关于TMS320C6713开发板25MHz有源晶振使用说明,晶诺威科技介绍如下: 针对TMS320C6713开发板使用25MHz有源晶振,核心的考量在于电平匹配、硬件连接方式以及芯片工作模式的配置。该型号有源晶振本身是一个完整的振荡器,输出的是稳定的CMOS方波,与无源晶振需要DSP内部振荡电路驱动…时间:2026/04/26

TMS320C6713开发板25MHz有源晶振使用说明

关于TMS320C6713开发板25MHz有源晶振使用说明,晶诺威科技介绍如下: 针对TMS320C6713开发板使用25MHz有源晶振,核心的考量在于电平匹配、硬件连接方式以及芯片工作模式的配置。该型号有源晶振本身是一个完整的振荡器,输出的是稳定的CMOS方波,与无源晶振需要DSP内部振荡电路驱动…时间:2026/04/26 -

; ) 为什么12pF负载的晶振外接6.8pF电容?

为什么12pF负载的晶振外接6.8pF电容? 对于负载电容( CL = 12pF ) 的晶振,外接 6.8pF 的电容通常是偏小的,但具体情况要看是“对地电容”还是“负载电容”。 为了让你更清楚,晶诺威科技分析三种情况如下: 1、 如果 6.8pF 是指“两个外接对地电容”的容值 这是最常见的情况。…时间:2026/04/23

为什么12pF负载的晶振外接6.8pF电容?

为什么12pF负载的晶振外接6.8pF电容? 对于负载电容( CL = 12pF ) 的晶振,外接 6.8pF 的电容通常是偏小的,但具体情况要看是“对地电容”还是“负载电容”。 为了让你更清楚,晶诺威科技分析三种情况如下: 1、 如果 6.8pF 是指“两个外接对地电容”的容值 这是最常见的情况。…时间:2026/04/23 -

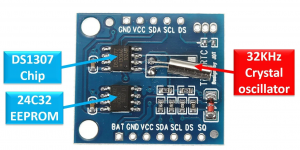

; ) 如何通过调节负载电容来调节时间快慢?

如何通过调节负载电容来调节时间快慢? 答:增大负载电容(CL1&CL2),钟表会走慢;减小负载电容(CL1&CL2),钟表会走快。 原理 石英钟表依靠石英晶振产生32768Hz的基准频率。这个频率并非固定不变,它会随着外接负载电容的变化而轻微偏移。 电容增大 → 晶振的谐振频率降低 …时间:2026/04/22

如何通过调节负载电容来调节时间快慢?

如何通过调节负载电容来调节时间快慢? 答:增大负载电容(CL1&CL2),钟表会走慢;减小负载电容(CL1&CL2),钟表会走快。 原理 石英钟表依靠石英晶振产生32768Hz的基准频率。这个频率并非固定不变,它会随着外接负载电容的变化而轻微偏移。 电容增大 → 晶振的谐振频率降低 …时间:2026/04/22 -

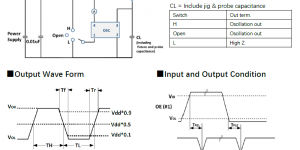

; ) 关于晶振Output Level输出电平的解释说明

关于晶振Output Level输出电平,晶诺威科技解释如下: 晶振的“输出电平”,简单来说,它是晶振输出信号的电压标准,决定了信号如何被数字电路识别为“0”或“1”。 为了帮助你更清晰地理解,我们需要将“无源晶振”和“有源晶振”分开来看,因为它们在输出电平上的表现完全不同。 1、 无源晶振:本身不…时间:2026/04/21

关于晶振Output Level输出电平的解释说明

关于晶振Output Level输出电平,晶诺威科技解释如下: 晶振的“输出电平”,简单来说,它是晶振输出信号的电压标准,决定了信号如何被数字电路识别为“0”或“1”。 为了帮助你更清晰地理解,我们需要将“无源晶振”和“有源晶振”分开来看,因为它们在输出电平上的表现完全不同。 1、 无源晶振:本身不…时间:2026/04/21 -

; ) 更换32.768khz晶振谐振电阻带来的可能性影响

关于更换32.768khz晶振谐振电阻带来的可能性影响,晶诺威科技分析及总结如下: 如果新晶振32.768kHz的谐振电阻(ESR,即等效串联电阻) 与原来的不匹配,可能会带来一系列影响。这个参数是晶振的核心指标之一,它直接关系到时钟电路能否稳定、准确地工作。 理想情况下,新晶振的谐振电阻应与原晶振…时间:2026/04/18

更换32.768khz晶振谐振电阻带来的可能性影响

关于更换32.768khz晶振谐振电阻带来的可能性影响,晶诺威科技分析及总结如下: 如果新晶振32.768kHz的谐振电阻(ESR,即等效串联电阻) 与原来的不匹配,可能会带来一系列影响。这个参数是晶振的核心指标之一,它直接关系到时钟电路能否稳定、准确地工作。 理想情况下,新晶振的谐振电阻应与原晶振…时间:2026/04/18 -

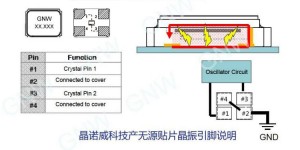

; ) 贴片无源晶振金属外壳与引脚接触会导致波形畸变吗?

贴片无源晶振金属外壳与引脚接触会导致波形畸变吗? 答:是的,如果贴片无源晶振的金属外壳与其频率引脚接触(短路)会直接导致波形畸变,甚至造成停振,使电路完全失效。 一、为什么会导致波形畸变或停振? 无源晶振依赖其两个频率引脚(通常为#1和#3)与外部电路产生谐振来生成时钟信号。如果金属外壳与任一频率引…时间:2026/04/16

贴片无源晶振金属外壳与引脚接触会导致波形畸变吗?

贴片无源晶振金属外壳与引脚接触会导致波形畸变吗? 答:是的,如果贴片无源晶振的金属外壳与其频率引脚接触(短路)会直接导致波形畸变,甚至造成停振,使电路完全失效。 一、为什么会导致波形畸变或停振? 无源晶振依赖其两个频率引脚(通常为#1和#3)与外部电路产生谐振来生成时钟信号。如果金属外壳与任一频率引…时间:2026/04/16 -

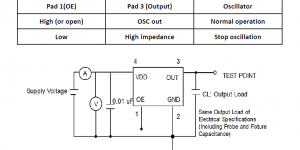

; ) OSC3225有源晶振PCB怎样布线更合理?

OSC3225有源晶振PCB怎样布线更合理? 为OSC3225有源晶振布局布线时,目标很明确:给它提供一个干净的“稳定的电源和一条畅通的“路”(纯净的输出)。它和无源晶振的布线策略有很大不同,核心在于处理好电源和地。 关于OSC3225有源晶振的PCB布线要点,晶诺威科技归纳如下: 1、 电源处理:…时间:2026/04/15

OSC3225有源晶振PCB怎样布线更合理?

OSC3225有源晶振PCB怎样布线更合理? 为OSC3225有源晶振布局布线时,目标很明确:给它提供一个干净的“稳定的电源和一条畅通的“路”(纯净的输出)。它和无源晶振的布线策略有很大不同,核心在于处理好电源和地。 关于OSC3225有源晶振的PCB布线要点,晶诺威科技归纳如下: 1、 电源处理:…时间:2026/04/15 -

; ) SMD3225无源晶振PCB怎样布线?

SMD3225无源晶振PCB怎样布线? 针对 SMD3225无源晶振的 PCB 布线要点,晶诺威科技建议如下: 1、 负载电容的位置:越近越好 通常情况下,无源晶振需要在两个正确匹配的外接电容的协助下才能正常工作。这两个电容在 PCB 上的摆放位置非常重要:这两个电容应该放在晶振和芯片的同一侧,且尽…时间:2026/04/13

SMD3225无源晶振PCB怎样布线?

SMD3225无源晶振PCB怎样布线? 针对 SMD3225无源晶振的 PCB 布线要点,晶诺威科技建议如下: 1、 负载电容的位置:越近越好 通常情况下,无源晶振需要在两个正确匹配的外接电容的协助下才能正常工作。这两个电容在 PCB 上的摆放位置非常重要:这两个电容应该放在晶振和芯片的同一侧,且尽…时间:2026/04/13