-

; ) RTC晶振32.768KHz精度该如何调整?

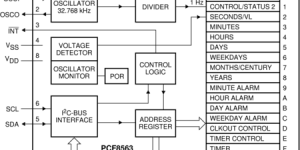

(PCF8563:实时时钟/日历) 首先,需要指出的是,RTC的主要作用是提供准确的时间基准,计时不准的RTC将失去其本质意义。 目前,部分芯片内部已集成RTC,实际测试中在电池供电6小时环境下芯片内部RTC的偏差大约在1-2分钟。因此,若对RTC实时时钟有更高的要求则需优先考虑外扩RTC,同时要求…时间:2021/11/26

RTC晶振32.768KHz精度该如何调整?

(PCF8563:实时时钟/日历) 首先,需要指出的是,RTC的主要作用是提供准确的时间基准,计时不准的RTC将失去其本质意义。 目前,部分芯片内部已集成RTC,实际测试中在电池供电6小时环境下芯片内部RTC的偏差大约在1-2分钟。因此,若对RTC实时时钟有更高的要求则需优先考虑外扩RTC,同时要求…时间:2021/11/26 -

; ) 32.768KHz晶振负载电容CL选错导致晶振不起振案例分析

(SMART LOCK:智能锁) 客户反馈在批量生产阶段,32.768KHz晶振不起振,导致所生产的智能锁开机系统紊乱,无法正常使用。 通过与客户沟通,了解到:该类型智能锁开机后,芯片捕捉32.768KHz晶振提供的时钟信号,完成系统诊断无误后,方可正常开机。问题就发生在芯片捕捉时钟信号失败这个环节…时间:2021/11/25

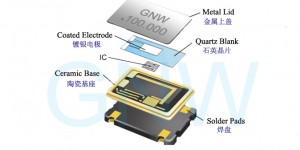

32.768KHz晶振负载电容CL选错导致晶振不起振案例分析

(SMART LOCK:智能锁) 客户反馈在批量生产阶段,32.768KHz晶振不起振,导致所生产的智能锁开机系统紊乱,无法正常使用。 通过与客户沟通,了解到:该类型智能锁开机后,芯片捕捉32.768KHz晶振提供的时钟信号,完成系统诊断无误后,方可正常开机。问题就发生在芯片捕捉时钟信号失败这个环节…时间:2021/11/25 -

; ) 低温环境下晶振性能不稳定如何解决?

涉及到晶振的工作温度,那就需要注意晶振两个参数指标:温度频差及工作温度。 晶诺威科技制造的耐低温晶振可选参数如下: 晶振工作温度: -20°C -30°C -40°C 晶振温度频差: ±10PPM ±20PPM ±30PPM 晶振在更低温下保持性能稳定一直是晶振领域研发之难题,主要原因之一是由石英晶…时间:2021/11/24

低温环境下晶振性能不稳定如何解决?

涉及到晶振的工作温度,那就需要注意晶振两个参数指标:温度频差及工作温度。 晶诺威科技制造的耐低温晶振可选参数如下: 晶振工作温度: -20°C -30°C -40°C 晶振温度频差: ±10PPM ±20PPM ±30PPM 晶振在更低温下保持性能稳定一直是晶振领域研发之难题,主要原因之一是由石英晶…时间:2021/11/24 -

; ) 关于有源晶振不稳定问题

在大多数情况下,与无源晶振相比,有源晶振的突出优势就是输出频率稳定度高,且更为精准,其原因是有源晶振已内置含IC在内的最佳匹配振荡电路,提供额定电压即可稳定输出主控芯片所需时钟信号。 关于有源晶振不稳定问题,可以从实际应用及有源晶振本身品质着手分析: 在有源晶振应用方面 请确保给有源晶振输入的电压在…时间:2021/11/23

关于有源晶振不稳定问题

在大多数情况下,与无源晶振相比,有源晶振的突出优势就是输出频率稳定度高,且更为精准,其原因是有源晶振已内置含IC在内的最佳匹配振荡电路,提供额定电压即可稳定输出主控芯片所需时钟信号。 关于有源晶振不稳定问题,可以从实际应用及有源晶振本身品质着手分析: 在有源晶振应用方面 请确保给有源晶振输入的电压在…时间:2021/11/23 -

; ) 单片机晶振时钟信号复位电路的作用及工作原理

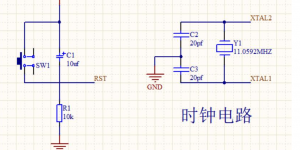

(单片机晶振时钟复位电路) 使单片机的状态处于初始化状态,让单片机的程序从头开始执行,获取晶振提供的时钟信号时处于稳定状态、各种寄存器、端口处于初始化状态等,其目的是让单片机能够稳定、正确的从头开始执行程序。 正常工作为高电平,低电平复位。 当单片机上电瞬间由于电容电压不能突变会使电容两边的电位相同…时间:2021/11/23

单片机晶振时钟信号复位电路的作用及工作原理

(单片机晶振时钟复位电路) 使单片机的状态处于初始化状态,让单片机的程序从头开始执行,获取晶振提供的时钟信号时处于稳定状态、各种寄存器、端口处于初始化状态等,其目的是让单片机能够稳定、正确的从头开始执行程序。 正常工作为高电平,低电平复位。 当单片机上电瞬间由于电容电压不能突变会使电容两边的电位相同…时间:2021/11/23 -

; ) 无源晶振/石英晶体谐振器输出频率测量方法

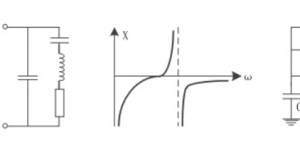

关于无源晶振/石英晶体谐振器输出频率测量方法,晶诺威科技解释如下: 无源晶振又被称之为Crystal(晶体、石英晶体谐振器),有源晶振则叫Oscillator(石英晶体振荡器)。 无源晶振是在石英晶片的两端镀上电极而成,其两管脚是无极性的。无源晶振自身无法起振,在工作时需要搭配外围电路。在一定条件下…时间:2021/11/22

无源晶振/石英晶体谐振器输出频率测量方法

关于无源晶振/石英晶体谐振器输出频率测量方法,晶诺威科技解释如下: 无源晶振又被称之为Crystal(晶体、石英晶体谐振器),有源晶振则叫Oscillator(石英晶体振荡器)。 无源晶振是在石英晶片的两端镀上电极而成,其两管脚是无极性的。无源晶振自身无法起振,在工作时需要搭配外围电路。在一定条件下…时间:2021/11/22 -

; ) 有源晶振时钟信号输出测试方法

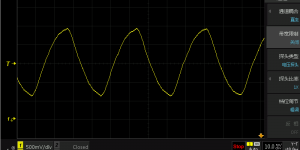

(图1) 举例:PCB板上的有源晶振输出时钟信号为25MHz或27MHz的方波。 当示波器的测量带宽较低时,方波的很多高频谐波分量会被滤除,此时看起来会比较像正弦波。 根据傅立叶展开公式,方波是由一系列正弦分量叠加而成的,称为各次谐波,且完美的方波只有1、3、5、7... 奇次谐波,无偶次谐波。公式…时间:2021/11/22

有源晶振时钟信号输出测试方法

(图1) 举例:PCB板上的有源晶振输出时钟信号为25MHz或27MHz的方波。 当示波器的测量带宽较低时,方波的很多高频谐波分量会被滤除,此时看起来会比较像正弦波。 根据傅立叶展开公式,方波是由一系列正弦分量叠加而成的,称为各次谐波,且完美的方波只有1、3、5、7... 奇次谐波,无偶次谐波。公式…时间:2021/11/22 -

; ) 由晶振12M引起的插卡音箱播放功能故障

音箱故障表述 电源指示灯亮,但U盘插入后,红灯一直闪烁,无法进入“绿灯”正常模式,音量旋钮无反应,歌曲无法播放,音箱无声音。 维修建议 尝试更换12MHz晶振 晶振12MHz工作原理 晶振12MHz的功能是为芯片提供频率信号,主要功能是协助芯片解码U盘或存储卡内部的音频文件。若12MHz晶振损坏,即…时间:2021/11/22

由晶振12M引起的插卡音箱播放功能故障

音箱故障表述 电源指示灯亮,但U盘插入后,红灯一直闪烁,无法进入“绿灯”正常模式,音量旋钮无反应,歌曲无法播放,音箱无声音。 维修建议 尝试更换12MHz晶振 晶振12MHz工作原理 晶振12MHz的功能是为芯片提供频率信号,主要功能是协助芯片解码U盘或存储卡内部的音频文件。若12MHz晶振损坏,即…时间:2021/11/22 -

; ) 3.6864MHz晶振低温不起振原因及对策

3.6864MHz晶振一般采用的为无源直插晶振49S或49SMD,属于低频晶体谐振器,即无源晶振。 (晶诺威科技3.6864MHz无源贴片晶振49SMD产品图) 关于3.6864MHz晶振低温不起振原因,晶诺威科技分析如下: 1、低频晶振的石英晶片较厚,等效阻抗比较大,因此在实际应用中需要注意等效阻…时间:2021/11/18

3.6864MHz晶振低温不起振原因及对策

3.6864MHz晶振一般采用的为无源直插晶振49S或49SMD,属于低频晶体谐振器,即无源晶振。 (晶诺威科技3.6864MHz无源贴片晶振49SMD产品图) 关于3.6864MHz晶振低温不起振原因,晶诺威科技分析如下: 1、低频晶振的石英晶片较厚,等效阻抗比较大,因此在实际应用中需要注意等效阻…时间:2021/11/18 -

; ) 无源晶振频偏案例及调校措施

(显示器显像故障) 设备不良现象表现为显示器不出彩或彩条等问题。在排除ISP(Image Signal Processing 图像信号处理系统)自身寄存器设定与TV Decoder输出周边參数不对的因素外,电路应用中的问题很有可能为晶振频偏所致。 举例:某款安防视频监控采用的晶振规格参数如下: 晶振…时间:2021/11/16

无源晶振频偏案例及调校措施

(显示器显像故障) 设备不良现象表现为显示器不出彩或彩条等问题。在排除ISP(Image Signal Processing 图像信号处理系统)自身寄存器设定与TV Decoder输出周边參数不对的因素外,电路应用中的问题很有可能为晶振频偏所致。 举例:某款安防视频监控采用的晶振规格参数如下: 晶振…时间:2021/11/16