-

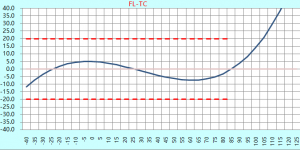

; ) 贴片晶振SMD3225-24M-9PF频率及电阻温测数据

(贴片晶振SMD3225-24M-9PF在温测中的频率变化) (贴片晶振SMD3225-24M-9PF在温测中的电阻变化) 贴片晶振SMD3225-24M-9PF频率及电阻温测数据如下: 针对晶振单体温测的必要性: 1、确保晶振在指定工作温度区间内没有发生电阻跳变,防止晶振起振困难或停…时间:2022/12/21

贴片晶振SMD3225-24M-9PF频率及电阻温测数据

(贴片晶振SMD3225-24M-9PF在温测中的频率变化) (贴片晶振SMD3225-24M-9PF在温测中的电阻变化) 贴片晶振SMD3225-24M-9PF频率及电阻温测数据如下: 针对晶振单体温测的必要性: 1、确保晶振在指定工作温度区间内没有发生电阻跳变,防止晶振起振困难或停…时间:2022/12/21 -

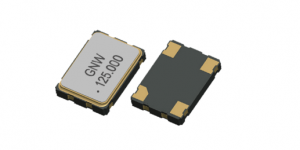

; ) 车载摄像头专用有源晶体振荡器OSC3225 37.125MHz/27MHz

晶诺威科技产OSC3225 37.125M/27MHz是一款协助设备实现屏显功能的常用有源晶振,主要电气参数如下: 输入电压:1.8V、2.8V、3.3V或5.0V 输出类型:CMOS 总频差:±20PPM 工作温度:-40~+85℃ OSC3225 37.125M/27MHz特点及优势: 宽温、高…时间:2022/12/20

车载摄像头专用有源晶体振荡器OSC3225 37.125MHz/27MHz

晶诺威科技产OSC3225 37.125M/27MHz是一款协助设备实现屏显功能的常用有源晶振,主要电气参数如下: 输入电压:1.8V、2.8V、3.3V或5.0V 输出类型:CMOS 总频差:±20PPM 工作温度:-40~+85℃ OSC3225 37.125M/27MHz特点及优势: 宽温、高…时间:2022/12/20 -

; ) 相噪与有源晶振性能之间的关系是什么?

相位噪声(phase noise),简称相噪,是有源晶振的一项非常重要的性能特征。它对作为振荡器的有源晶振的输出频率稳定性影响非常大,一般情况下,相位噪声越小,则表示有源晶振性能越好,输出信号稳定性越高。 相位噪声对振荡电路的影响 有源晶振的Q值对于改善相位噪声的载波频率附近的相位噪声尤其重要。无论…时间:2022/12/19

相噪与有源晶振性能之间的关系是什么?

相位噪声(phase noise),简称相噪,是有源晶振的一项非常重要的性能特征。它对作为振荡器的有源晶振的输出频率稳定性影响非常大,一般情况下,相位噪声越小,则表示有源晶振性能越好,输出信号稳定性越高。 相位噪声对振荡电路的影响 有源晶振的Q值对于改善相位噪声的载波频率附近的相位噪声尤其重要。无论…时间:2022/12/19 -

; ) 关于TCXO温补晶振常见解决方案及选型注意事项

关于TCXO温补晶振常见解决方案及选型注意事项,总结如下: MU 指对一次互感器传输过来的电气量进行合并和同步处理,并将处理后的数字信号按照特定格式转发给间隔级设备使用的装置。 MU是电子式电流、电压互感器的接口装置。MU在一定程度上实现了过程层数据的共享和数字化,它作为遵循IEC61850标准的数…时间:2022/12/16

关于TCXO温补晶振常见解决方案及选型注意事项

关于TCXO温补晶振常见解决方案及选型注意事项,总结如下: MU 指对一次互感器传输过来的电气量进行合并和同步处理,并将处理后的数字信号按照特定格式转发给间隔级设备使用的装置。 MU是电子式电流、电压互感器的接口装置。MU在一定程度上实现了过程层数据的共享和数字化,它作为遵循IEC61850标准的数…时间:2022/12/16 -

; ) 12.5PF的晶体匹配电容是多少PF?

匹配电容的变化对晶体输出频率的影响: 匹配电容容值增加,晶体输出频率降低。 匹配电容容值减小,晶体输出频率升高。 如果晶体负载电容CL为12.5PF,晶诺威科技建议匹配电容在15~18PF之间取值。但在晶体实际电路应用中,也有匹配22PF为最佳的情况,这主要归因于电路板本身之间的差异。 匹配电容对晶…时间:2022/12/14

12.5PF的晶体匹配电容是多少PF?

匹配电容的变化对晶体输出频率的影响: 匹配电容容值增加,晶体输出频率降低。 匹配电容容值减小,晶体输出频率升高。 如果晶体负载电容CL为12.5PF,晶诺威科技建议匹配电容在15~18PF之间取值。但在晶体实际电路应用中,也有匹配22PF为最佳的情况,这主要归因于电路板本身之间的差异。 匹配电容对晶…时间:2022/12/14 -

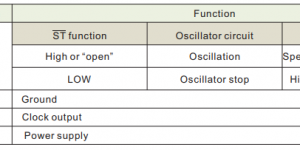

; ) 晶体振荡器(OSC5032/OSC7050)功耗及待机电流介绍

Pin functions for Oscillators 晶诺威产晶体振荡器(OSC5032/OSC7050)功耗及待机电流介绍如下: 晶体振荡器(OSC5032/OSC7050)Supply consumption功耗 22mA max. (@1.8V) 25mA max. (@2.5V) 35…时间:2022/12/09

晶体振荡器(OSC5032/OSC7050)功耗及待机电流介绍

Pin functions for Oscillators 晶诺威产晶体振荡器(OSC5032/OSC7050)功耗及待机电流介绍如下: 晶体振荡器(OSC5032/OSC7050)Supply consumption功耗 22mA max. (@1.8V) 25mA max. (@2.5V) 35…时间:2022/12/09 -

; ) 有源晶振OE功能Logic 1 or Open及Logic 0是什么意思?

我们可能会在有源晶振规格书中见到以下英语: Output will be enable if OE is Logic 1 or Open; Output will be disable if OE is Logic 0. 中文内容如下: 如果OE选择Logic 1(逻辑1)或open(打开),频率信…时间:2022/12/07

有源晶振OE功能Logic 1 or Open及Logic 0是什么意思?

我们可能会在有源晶振规格书中见到以下英语: Output will be enable if OE is Logic 1 or Open; Output will be disable if OE is Logic 0. 中文内容如下: 如果OE选择Logic 1(逻辑1)或open(打开),频率信…时间:2022/12/07 -

; ) 关于恒温晶振OCXO与时钟源层级Stratum定义

NTP使用一个分层、半分层的时间源系统。该时钟层次的每个级别被称为“stratum”,顶层分配为数字0。一个通过阶层n同步的服务器将运行在阶层n + 1。数字表示与参考时钟的距离,用于防止层次结构中的循环依赖性。阶层并不总是指示质量或可靠性;在阶层3的时间源得到比阶层2时间源更高的时间质量也很常见。…时间:2022/11/30

关于恒温晶振OCXO与时钟源层级Stratum定义

NTP使用一个分层、半分层的时间源系统。该时钟层次的每个级别被称为“stratum”,顶层分配为数字0。一个通过阶层n同步的服务器将运行在阶层n + 1。数字表示与参考时钟的距离,用于防止层次结构中的循环依赖性。阶层并不总是指示质量或可靠性;在阶层3的时间源得到比阶层2时间源更高的时间质量也很常见。…时间:2022/11/30 -

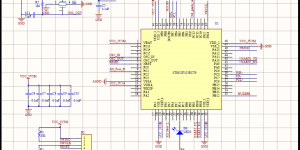

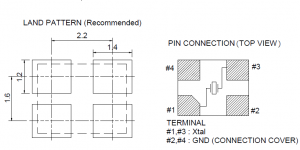

; ) 关于有源晶振测试电路及测试条件的说明

以晶诺威产SMD 3225贴片有源晶振(CMOS输出)为例: #1脚为OE功能端,三态功能的开关。 #2脚GND为接地端。 #3脚Output为频率输出端。 #4脚Vdd是工作电压输入端。 在电路设计焊接中,为了稳定运行,建议在Vdd和GND之间连接0.01μF至0.1μF的旁路电容,并尽可能靠近V…时间:2022/11/26

关于有源晶振测试电路及测试条件的说明

以晶诺威产SMD 3225贴片有源晶振(CMOS输出)为例: #1脚为OE功能端,三态功能的开关。 #2脚GND为接地端。 #3脚Output为频率输出端。 #4脚Vdd是工作电压输入端。 在电路设计焊接中,为了稳定运行,建议在Vdd和GND之间连接0.01μF至0.1μF的旁路电容,并尽可能靠近V…时间:2022/11/26 -

; ) 关于晶体谐振器(晶体)的使用说明

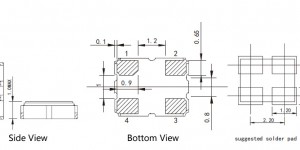

(SMD3225-4PIN晶体谐振器尺寸及引脚说明) 关于晶体谐振器(晶体)的使用说明 Since the crystal unit is a passive component, it is important to have appropriate circuit conditions. Ple…时间:2022/11/21

关于晶体谐振器(晶体)的使用说明

(SMD3225-4PIN晶体谐振器尺寸及引脚说明) 关于晶体谐振器(晶体)的使用说明 Since the crystal unit is a passive component, it is important to have appropriate circuit conditions. Ple…时间:2022/11/21