-

; ) 影响晶振频率稳定的因素及改善措施

晶振是一种用于稳定频率和选择频率的重要电子元件。 所谓频率稳定,就是在各种外界条件发生变化时,晶振实际工作频率与指定频率之间偏差最小,稳定的振荡频率,才能使一些电路对信号能够正确处理准确输出,影响晶振频率稳定的主要因素。 一般情况下,影响因素主要有以下三种: 温度(Temperature) 环境温度…时间:2022/05/11

影响晶振频率稳定的因素及改善措施

晶振是一种用于稳定频率和选择频率的重要电子元件。 所谓频率稳定,就是在各种外界条件发生变化时,晶振实际工作频率与指定频率之间偏差最小,稳定的振荡频率,才能使一些电路对信号能够正确处理准确输出,影响晶振频率稳定的主要因素。 一般情况下,影响因素主要有以下三种: 温度(Temperature) 环境温度…时间:2022/05/11 -

; ) 8MHz无源晶振典型电路:8MHz晶振需要匹配多大电容?

(贴片式无源晶振SMD3225-4 pads) 晶诺威科技生产的贴片无源晶振8M常见负载电容CL为12PF和20PF,建议如下: 当晶振负载电容CL=12PF时,建议匹配电容在15-18PF之间。 当晶振负载电容CL=20PF时,建议匹配电容在27-33PF之间。 由以上可见,8MHz…时间:2022/05/11

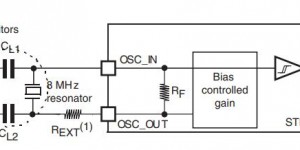

8MHz无源晶振典型电路:8MHz晶振需要匹配多大电容?

(贴片式无源晶振SMD3225-4 pads) 晶诺威科技生产的贴片无源晶振8M常见负载电容CL为12PF和20PF,建议如下: 当晶振负载电容CL=12PF时,建议匹配电容在15-18PF之间。 当晶振负载电容CL=20PF时,建议匹配电容在27-33PF之间。 由以上可见,8MHz…时间:2022/05/11 -

; ) 关于晶体振荡器/有源晶振驱动能力的说明

关于晶体振荡器/有源晶振驱动能力的说明如下: 首先,高驱动能力意味着高功耗。不要期望只能额定驱动15pF的晶体振荡器在驱动30pF或50pF时会有好的表现。负载越大,功耗越大,驱动能力越强,比如常用于工控设备的晶体振荡器,若输出负载为30PF,则输入电压一般为5V。 对于需要电池供电的电子设备,一定…时间:2022/05/10

关于晶体振荡器/有源晶振驱动能力的说明

关于晶体振荡器/有源晶振驱动能力的说明如下: 首先,高驱动能力意味着高功耗。不要期望只能额定驱动15pF的晶体振荡器在驱动30pF或50pF时会有好的表现。负载越大,功耗越大,驱动能力越强,比如常用于工控设备的晶体振荡器,若输出负载为30PF,则输入电压一般为5V。 对于需要电池供电的电子设备,一定…时间:2022/05/10 -

; ) 有关晶诺威科技产SMD贴片晶振产品软焊说明

晶诺威科技产SMD贴片晶振产品的软焊温度条件被设计成可以和普通电子零部件同时作业,但如果是超过规格以上的高温,则频率有可能发生较大的变化,因此请避免不必要的高温度。 有关本公司产SMD贴片晶振产品的回流焊焊接温度描述,请参照下图。 回流焊焊接温度描述(支持无铅焊锡) ※ 回流焊焊接温度描述有可能根据…时间:2022/05/05

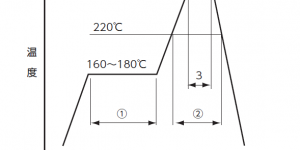

有关晶诺威科技产SMD贴片晶振产品软焊说明

晶诺威科技产SMD贴片晶振产品的软焊温度条件被设计成可以和普通电子零部件同时作业,但如果是超过规格以上的高温,则频率有可能发生较大的变化,因此请避免不必要的高温度。 有关本公司产SMD贴片晶振产品的回流焊焊接温度描述,请参照下图。 回流焊焊接温度描述(支持无铅焊锡) ※ 回流焊焊接温度描述有可能根据…时间:2022/05/05 -

; ) 关于晶体谐振器激励电平/激励功率的一点补充说明

合适的激励电平因晶体谐振器型号以及谐波次数的不同而存在差异。在晶诺威科技晶振谐振器规格书中,激励电平/激励功率的项目栏中记载的是最大规格值。 MHz晶体谐振器 基波模式:300μW max.、200μW max.、100μW max. 谐波模式:1mW max.、500μW max. KHz晶体谐振…时间:2022/05/05

关于晶体谐振器激励电平/激励功率的一点补充说明

合适的激励电平因晶体谐振器型号以及谐波次数的不同而存在差异。在晶诺威科技晶振谐振器规格书中,激励电平/激励功率的项目栏中记载的是最大规格值。 MHz晶体谐振器 基波模式:300μW max.、200μW max.、100μW max. 谐波模式:1mW max.、500μW max. KHz晶体谐振…时间:2022/05/05 -

; ) 晶体谐振器/无源晶振振荡电路设计六个注意要点

(晶体谐振器振荡电路设计图例) 晶体谐振器振荡电路设计六个注意要点归纳如下: 1、IC的选择 请务必选择与振荡频率相应的IC。 举例: 相当于4069UB : 从KHz带到8MHz附近 相当于7WU04 : 4~30MHz 相当于7WHU04 : 20~60MHz 2、反馈电阻Rf DC偏置用反馈电…时间:2022/05/05

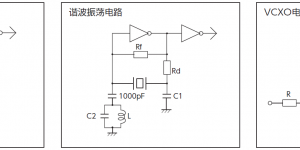

晶体谐振器/无源晶振振荡电路设计六个注意要点

(晶体谐振器振荡电路设计图例) 晶体谐振器振荡电路设计六个注意要点归纳如下: 1、IC的选择 请务必选择与振荡频率相应的IC。 举例: 相当于4069UB : 从KHz带到8MHz附近 相当于7WU04 : 4~30MHz 相当于7WHU04 : 20~60MHz 2、反馈电阻Rf DC偏置用反馈电…时间:2022/05/05 -

; ) 汽车中控锁低功耗HC-49S/SMD 4MHz晶振规格参数

汽车电子技术的智能化,如发动机控制、制动控制和转向控制,在先进的驾驶辅助系统(ADAS)中越来越不可或缺,其重要性也越来越大。它们都由电子控制单元(ECU)控制,电子控制单元是控制它们动作的时钟源定时装置。 其中,汽车中控锁对晶振有着严格的低功耗要求。针对于此,晶诺威科技研发及生产的低功耗无源晶振H…时间:2022/04/29

汽车中控锁低功耗HC-49S/SMD 4MHz晶振规格参数

汽车电子技术的智能化,如发动机控制、制动控制和转向控制,在先进的驾驶辅助系统(ADAS)中越来越不可或缺,其重要性也越来越大。它们都由电子控制单元(ECU)控制,电子控制单元是控制它们动作的时钟源定时装置。 其中,汽车中控锁对晶振有着严格的低功耗要求。针对于此,晶诺威科技研发及生产的低功耗无源晶振H…时间:2022/04/29 -

; ) 关于低功耗晶振选择与低功耗晶振电路设计

对于一些只能提供有限电源的电路应用,我们不得不对晶振也提出低功耗的要求。有两种选择:无源晶振方案和有源晶振方案。 无源晶振低功耗方案 无源晶振实现低功耗的前提是:能够在较小激励功率之下正常起振且保持正常工作状态(频率稳定性)。在此条件之下,还需要考虑与时钟芯片的兼容性,比如,建议选择电压为1.8V的…时间:2022/04/28

关于低功耗晶振选择与低功耗晶振电路设计

对于一些只能提供有限电源的电路应用,我们不得不对晶振也提出低功耗的要求。有两种选择:无源晶振方案和有源晶振方案。 无源晶振低功耗方案 无源晶振实现低功耗的前提是:能够在较小激励功率之下正常起振且保持正常工作状态(频率稳定性)。在此条件之下,还需要考虑与时钟芯片的兼容性,比如,建议选择电压为1.8V的…时间:2022/04/28 -

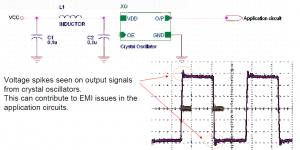

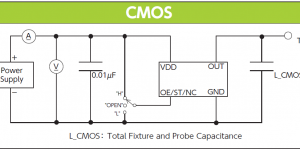

; ) 晶诺威科技产有源晶振EMI消除方案

晶诺威科技产有源晶振EMI消除方案解释如下: 1、由下图可见有源晶振输出信号中出现电压尖峰,这可能会给应用电路带来EMI问题。如下图所示: 2、晶诺威科技建议在时钟信号输出端和 GND 之间添加旁路电容( 5-10 pF ),可以使输出波形平滑化,并可显著降低EMI。如下图所示:时间:2022/04/27

晶诺威科技产有源晶振EMI消除方案

晶诺威科技产有源晶振EMI消除方案解释如下: 1、由下图可见有源晶振输出信号中出现电压尖峰,这可能会给应用电路带来EMI问题。如下图所示: 2、晶诺威科技建议在时钟信号输出端和 GND 之间添加旁路电容( 5-10 pF ),可以使输出波形平滑化,并可显著降低EMI。如下图所示:时间:2022/04/27

; )