-

; ) 晶诺威科技产无源贴片晶振EMI消除方案

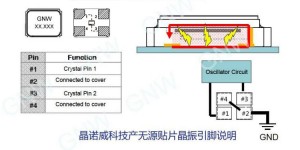

Terminals 2 and 4 on a Genuway crystal unit are connected electrically to the metal cover of the crystal. 晶诺威科技产无源贴片晶振焊盘#2和#4与金属外壳连接。 Genuway recommen…时间:2022/04/27

晶诺威科技产无源贴片晶振EMI消除方案

Terminals 2 and 4 on a Genuway crystal unit are connected electrically to the metal cover of the crystal. 晶诺威科技产无源贴片晶振焊盘#2和#4与金属外壳连接。 Genuway recommen…时间:2022/04/27 -

; ) 如何禁止有源晶振的三态功能Tri-State function?

(有源晶振的三态功能) If Tri-state function is not needed, the Tri-state pin shall be connected to the Vcc pin or left floating. There is an internal pullup res…时间:2022/04/27

如何禁止有源晶振的三态功能Tri-State function?

(有源晶振的三态功能) If Tri-state function is not needed, the Tri-state pin shall be connected to the Vcc pin or left floating. There is an internal pullup res…时间:2022/04/27 -

; ) 若晶振负载CL=16PF, 如何计算并联谐振电路中负载电容值?

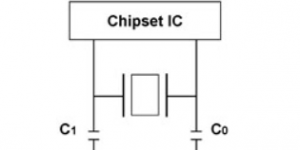

Cstray is the stray capacitance in the circuit, typically 3-5pF(as is supposed), and C1 and C0 are the external capacitors in the oscillator circuit. …时间:2022/04/27

若晶振负载CL=16PF, 如何计算并联谐振电路中负载电容值?

Cstray is the stray capacitance in the circuit, typically 3-5pF(as is supposed), and C1 and C0 are the external capacitors in the oscillator circuit. …时间:2022/04/27 -

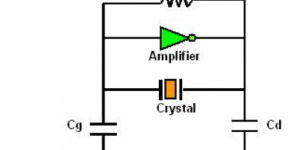

; ) 石英晶体振荡器电路和工作原理图解

(石英晶体与石英晶片) 石英晶体具有非常重要的特性,称为压电效应。当在晶体表面上施加机械压力时,与机械压力成比例的电压出现在晶体上。该电压会导致晶体失真。失真的量将与施加的电压成比例,并且与施加到晶体上的交流电压成正比,从而导致晶体以其固有频率振动。 晶体振荡器是一种电子振荡器电路,用于压电材料振动…时间:2022/04/26

石英晶体振荡器电路和工作原理图解

(石英晶体与石英晶片) 石英晶体具有非常重要的特性,称为压电效应。当在晶体表面上施加机械压力时,与机械压力成比例的电压出现在晶体上。该电压会导致晶体失真。失真的量将与施加的电压成比例,并且与施加到晶体上的交流电压成正比,从而导致晶体以其固有频率振动。 晶体振荡器是一种电子振荡器电路,用于压电材料振动…时间:2022/04/26 -

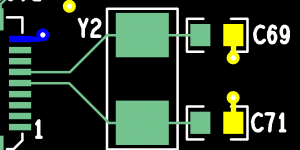

; ) 高速和低速晶振电路为何需要两个电容并接地?

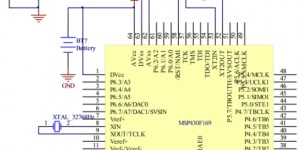

正常芯片及电路板都会存在4PF~6PF左右的杂散电容,因此: 接32.768KHz的无源晶振时,如果负载CL=12.5PF,建议外接电容18~22PF,并接地构成回路,否则时间容易产生过大偏差。 接8MHz的无源晶振时,若负载CL=12PF,建议外接电容15PF;若负载CL=20PF,建议外接电容2…时间:2022/04/25

高速和低速晶振电路为何需要两个电容并接地?

正常芯片及电路板都会存在4PF~6PF左右的杂散电容,因此: 接32.768KHz的无源晶振时,如果负载CL=12.5PF,建议外接电容18~22PF,并接地构成回路,否则时间容易产生过大偏差。 接8MHz的无源晶振时,若负载CL=12PF,建议外接电容15PF;若负载CL=20PF,建议外接电容2…时间:2022/04/25 -

; ) 进口工控有源晶振国产化替代方案

关于进口工控有源晶振国产化替代,以下重要电气参数值得关注: 温度频差Frequency Stability vs Temperature ±10ppm、±20ppm、±30ppm 工作温度范围Operating Temperature Range -20~+70℃、-40~+85℃ 输出波型Outp…时间:2022/04/24

进口工控有源晶振国产化替代方案

关于进口工控有源晶振国产化替代,以下重要电气参数值得关注: 温度频差Frequency Stability vs Temperature ±10ppm、±20ppm、±30ppm 工作温度范围Operating Temperature Range -20~+70℃、-40~+85℃ 输出波型Outp…时间:2022/04/24 -

; ) 喇叭或蜂鸣器会干扰晶振正常工作吗?

喇叭或蜂鸣器会干扰晶振正常工作吗? 答:会!喇叭或蜂鸣器会干扰晶振正常工作。 任何周期性物理冲击或机械振动都会对晶振的输出频率及/或幅度造成不同程度的影响,比如:马达、压电扬声器、压电蜂鸣器、喇叭等。 当晶振的正常工作受到此类干扰时,可能造成设备工作不正常,如果是通信器材,则可能会发生通信故障。 在…时间:2022/04/22

喇叭或蜂鸣器会干扰晶振正常工作吗?

喇叭或蜂鸣器会干扰晶振正常工作吗? 答:会!喇叭或蜂鸣器会干扰晶振正常工作。 任何周期性物理冲击或机械振动都会对晶振的输出频率及/或幅度造成不同程度的影响,比如:马达、压电扬声器、压电蜂鸣器、喇叭等。 当晶振的正常工作受到此类干扰时,可能造成设备工作不正常,如果是通信器材,则可能会发生通信故障。 在…时间:2022/04/22 -

; ) How to calculate the CL? 如何计算负载电容CL?

(皮尔斯晶振振荡电路) How to calculate the CL? 如何计算负载电容CL? Use this formula to approximate the value of capacitors needed: 使用下面公式来估算所需的负载电容值: CL=((C1 x C2) / (C…时间:2022/04/19

How to calculate the CL? 如何计算负载电容CL?

(皮尔斯晶振振荡电路) How to calculate the CL? 如何计算负载电容CL? Use this formula to approximate the value of capacitors needed: 使用下面公式来估算所需的负载电容值: CL=((C1 x C2) / (C…时间:2022/04/19 -

; ) 晶诺威科技晶振产品常见问题及使用注意事项

晶振产品常见问题及使用注意事项归纳如下: 1.一般清洁溶液或超声波清洁(Ultrasonic cleaning)方法可用于清洁我司的晶振产品。但是,在某些情况下,超声波清洗机会在晶振产品的振荡频率下产生共振,从而造成晶振电气特性的恶化,甚至损坏晶振的整体结构。因此,建议在超声波清洁前进行验证测试。 …时间:2022/04/12

晶诺威科技晶振产品常见问题及使用注意事项

晶振产品常见问题及使用注意事项归纳如下: 1.一般清洁溶液或超声波清洁(Ultrasonic cleaning)方法可用于清洁我司的晶振产品。但是,在某些情况下,超声波清洗机会在晶振产品的振荡频率下产生共振,从而造成晶振电气特性的恶化,甚至损坏晶振的整体结构。因此,建议在超声波清洁前进行验证测试。 …时间:2022/04/12 -

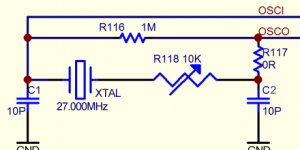

; ) 晶体CL和PCBA CL不匹配时会对实际输出频率有什么影响?

(CL=9PF的无源晶振27MHz,外接电容C1=C2=10PF) 晶体(无源晶振)CL和PCBA(电路板) CL的关系解释如下: We produce the crystal CL to satisfy the customer’s request. Nominal frequency means…时间:2022/04/12

晶体CL和PCBA CL不匹配时会对实际输出频率有什么影响?

(CL=9PF的无源晶振27MHz,外接电容C1=C2=10PF) 晶体(无源晶振)CL和PCBA(电路板) CL的关系解释如下: We produce the crystal CL to satisfy the customer’s request. Nominal frequency means…时间:2022/04/12