-

; ) 单片机中的时钟晶振起什么作用?

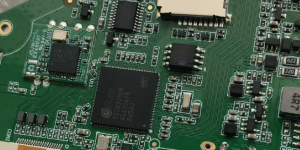

几乎每个单片机系统里都要用到时钟晶振,全称叫晶体振荡器。在单片机系统里时钟晶振的作用非常重要,它结合单片机内部的电路,产生单片机所必需的时钟频率,单片机所有指令的执行都是建立在这个基础之上。一般来说,晶振提供的时钟频率越高,单片机运行速度越快。 晶振通常与锁相环电路配合使用,以提供系统所需的时钟频率…时间:2021/10/20

单片机中的时钟晶振起什么作用?

几乎每个单片机系统里都要用到时钟晶振,全称叫晶体振荡器。在单片机系统里时钟晶振的作用非常重要,它结合单片机内部的电路,产生单片机所必需的时钟频率,单片机所有指令的执行都是建立在这个基础之上。一般来说,晶振提供的时钟频率越高,单片机运行速度越快。 晶振通常与锁相环电路配合使用,以提供系统所需的时钟频率…时间:2021/10/20 -

; ) 如果晶振不工作,电路会发生什么问题?

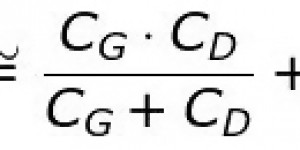

(晶振负载电容匹配公式) 晶振在电路中的作用就是为系统提供基本的频率时序信号,如果晶振不工作,MCU就会停止,导致整个电路都不能工作。分析如下: 频率偏移超出正常值。当电路中心频率正偏时,说明CL偏小,可以增加晶振外接电容Cd和Cg的值。当电路中心频率负偏时,说明CL偏大,可以减少晶振外接电容Cd和…时间:2021/10/19

如果晶振不工作,电路会发生什么问题?

(晶振负载电容匹配公式) 晶振在电路中的作用就是为系统提供基本的频率时序信号,如果晶振不工作,MCU就会停止,导致整个电路都不能工作。分析如下: 频率偏移超出正常值。当电路中心频率正偏时,说明CL偏小,可以增加晶振外接电容Cd和Cg的值。当电路中心频率负偏时,说明CL偏大,可以减少晶振外接电容Cd和…时间:2021/10/19 -

; ) 晶振频率的选择

芯片通常都会有一个最高工作频率要求,比如:Atmega48v(低功耗)最高8MHz,Atmega48a最高16Mhz,选择晶振时不要超过这个频率即可。 PLL的作用是倍频,可以*2,*3,*4……*16,其时钟信号通过选择器PLLSRC由MHz的高速内部RC振荡器经过二分频提供,也可由PLLXTPR…时间:2021/10/18

晶振频率的选择

芯片通常都会有一个最高工作频率要求,比如:Atmega48v(低功耗)最高8MHz,Atmega48a最高16Mhz,选择晶振时不要超过这个频率即可。 PLL的作用是倍频,可以*2,*3,*4……*16,其时钟信号通过选择器PLLSRC由MHz的高速内部RC振荡器经过二分频提供,也可由PLLXTPR…时间:2021/10/18 -

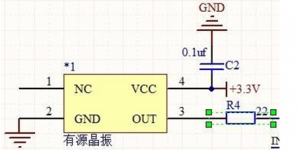

; ) 有源晶振的用法及使用注意事项

有源晶振通常的用法: 一脚悬空,二脚接地,三脚接输出,四脚接电压。 有源晶振的电压输入脚最好不要直连电源,而是通过一个磁珠后接入,这样可大大降低电源噪声对时钟输出频率的影响。有源晶振的电源去耦电容的匹配也很重要,去耦电容一般选三个,容值依次递减。 晶诺威科技产OSC3225有源晶振测试电路及引脚说明…时间:2021/10/16

有源晶振的用法及使用注意事项

有源晶振通常的用法: 一脚悬空,二脚接地,三脚接输出,四脚接电压。 有源晶振的电压输入脚最好不要直连电源,而是通过一个磁珠后接入,这样可大大降低电源噪声对时钟输出频率的影响。有源晶振的电源去耦电容的匹配也很重要,去耦电容一般选三个,容值依次递减。 晶诺威科技产OSC3225有源晶振测试电路及引脚说明…时间:2021/10/16 -

; ) 贴片晶体特点优势是什么?

贴片晶体特点优势 体积小,满足SMT自动化贴片 Q值高,输出频率精度高,稳定性强,功耗小且使用寿命长 耐湿性好,不易产生微裂现象 热冲击实验和温度循环实验后不产生损伤,机械强度高 热膨胀系数小,热导性高 绝缘性和气密性好,满足高密封要求 贴片晶体主要应用领域 射频、遥控载频、智能系统、通信网络、无线…时间:2021/10/15

贴片晶体特点优势是什么?

贴片晶体特点优势 体积小,满足SMT自动化贴片 Q值高,输出频率精度高,稳定性强,功耗小且使用寿命长 耐湿性好,不易产生微裂现象 热冲击实验和温度循环实验后不产生损伤,机械强度高 热膨胀系数小,热导性高 绝缘性和气密性好,满足高密封要求 贴片晶体主要应用领域 射频、遥控载频、智能系统、通信网络、无线…时间:2021/10/15 -

; ) 晶诺威科技2520贴片晶振特点及优势

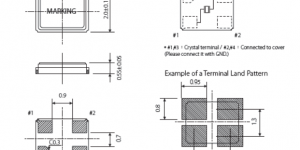

(晶诺威科技2520贴片晶振尺寸及焊盘示意图) 频率范围 f_nom=12.000MHz~50.000MHz 体积2.5x2.0x0.55mm 储存温度 T_stg -40℃~+125℃ (裸存) 工作温度 Tuse -40℃~+85°C (标准温度) 激励功率 DL= 10pW(100uW max…时间:2021/10/15

晶诺威科技2520贴片晶振特点及优势

(晶诺威科技2520贴片晶振尺寸及焊盘示意图) 频率范围 f_nom=12.000MHz~50.000MHz 体积2.5x2.0x0.55mm 储存温度 T_stg -40℃~+125℃ (裸存) 工作温度 Tuse -40℃~+85°C (标准温度) 激励功率 DL= 10pW(100uW max…时间:2021/10/15 -

; ) 如何根据晶振负载电容CL选择晶振?

假设您在两个无源晶振32MHz之间选择:一个为负载电容CL=12pF,另外一个是负载电容 CL=20pF,所有其它参数都相同且芯片针对这两种晶振都支持,您应该选择哪一个? 晶振的起振时间约在7~15毫秒。一般情况下,具备较低负载电容CL的晶振会有一个更快的起振时间,系统等待参时钟启动的时间更少,这样…时间:2021/10/14

如何根据晶振负载电容CL选择晶振?

假设您在两个无源晶振32MHz之间选择:一个为负载电容CL=12pF,另外一个是负载电容 CL=20pF,所有其它参数都相同且芯片针对这两种晶振都支持,您应该选择哪一个? 晶振的起振时间约在7~15毫秒。一般情况下,具备较低负载电容CL的晶振会有一个更快的起振时间,系统等待参时钟启动的时间更少,这样…时间:2021/10/14 -

; ) 32.768KHz晶振振荡电路原理及起振时间

振荡电路用于实时时钟RTC时,经常使用FC-135(SMD3215)、MC-146(SMD7015)贴片晶振或者圆柱体晶振连接在OSC32_IN与OSC32_OUT之间。为了获得稳定且精准的频率信号,必须外加两个合适的电容以构成振荡电路。当然,也可以选择内嵌振荡电路的有源系列32.768KHz晶体振…时间:2021/10/13

32.768KHz晶振振荡电路原理及起振时间

振荡电路用于实时时钟RTC时,经常使用FC-135(SMD3215)、MC-146(SMD7015)贴片晶振或者圆柱体晶振连接在OSC32_IN与OSC32_OUT之间。为了获得稳定且精准的频率信号,必须外加两个合适的电容以构成振荡电路。当然,也可以选择内嵌振荡电路的有源系列32.768KHz晶体振…时间:2021/10/13 -

; ) 晶振负载电容CL与振荡电路的关系

晶振负载电容CL与振荡电路的关系如下: 在无源晶振振荡电路中,必须创造足够的“负性阻抗”,以抵消从 ESR 和维持振荡的电流损失。晶振负载电容值 CL 不是振荡电路的一部分,而是晶振本身在制造中设定的固定值。 在无源晶振实际电路应用中,我们为了获得其共振后的目标频率,必须加载该电容CL 。如果你使用…时间:2021/10/12

晶振负载电容CL与振荡电路的关系

晶振负载电容CL与振荡电路的关系如下: 在无源晶振振荡电路中,必须创造足够的“负性阻抗”,以抵消从 ESR 和维持振荡的电流损失。晶振负载电容值 CL 不是振荡电路的一部分,而是晶振本身在制造中设定的固定值。 在无源晶振实际电路应用中,我们为了获得其共振后的目标频率,必须加载该电容CL 。如果你使用…时间:2021/10/12 -

; ) 芯片时序OSC接口指的是什么?

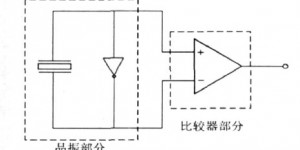

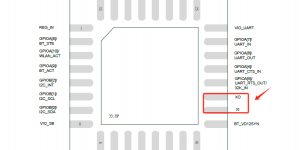

芯片OSC接口功能是指需要外接晶振构成振荡器,其目的是给芯片提供时钟信号。 OSC为Oscillator的英文缩写,意为晶体振荡器。晶体振荡器是一种能量转换装置,即将直流电能转换为具有指定频率的交流电能,其构成的电路叫振荡电路。 无源晶振与有源晶振振荡电路对比如下: (8MHz无源晶振振荡电路图例)…时间:2021/10/11

芯片时序OSC接口指的是什么?

芯片OSC接口功能是指需要外接晶振构成振荡器,其目的是给芯片提供时钟信号。 OSC为Oscillator的英文缩写,意为晶体振荡器。晶体振荡器是一种能量转换装置,即将直流电能转换为具有指定频率的交流电能,其构成的电路叫振荡电路。 无源晶振与有源晶振振荡电路对比如下: (8MHz无源晶振振荡电路图例)…时间:2021/10/11