-

; ) 有源晶振输出方波变形成振铃怎么解决?

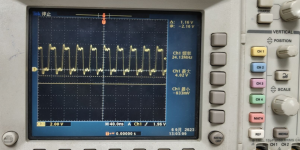

有源晶振输出方波变形成振铃怎么解决? 有源晶振输出方波变形成振铃通常不是一个故障,而是信号完整性问题的典型表现。晶诺威科技详解如下: 一、 什么是“振铃”? 振铃是指方波信号在跳变沿(上升沿或下降沿)后,出现的一系列幅度逐渐衰减的振荡,形状类似于铃铛被敲击后的声音波形,因此得名。 正常的理想方波: …时间:2026/03/07

有源晶振输出方波变形成振铃怎么解决?

有源晶振输出方波变形成振铃怎么解决? 有源晶振输出方波变形成振铃通常不是一个故障,而是信号完整性问题的典型表现。晶诺威科技详解如下: 一、 什么是“振铃”? 振铃是指方波信号在跳变沿(上升沿或下降沿)后,出现的一系列幅度逐渐衰减的振荡,形状类似于铃铛被敲击后的声音波形,因此得名。 正常的理想方波: …时间:2026/03/07 -

; ) 有源晶振输出幅度怎么调整?

有源晶振输出幅度怎么调整?晶诺威科技解释如下: 有源晶振是完整的振荡器,其输出幅度主要由内部电路设计决定,在出厂时已固定。用户端的调整空间有限,且主要是衰减而非增强。 有源晶振的输出类型是选型时就必须确定的,它直接决定了幅度: CMOS:最常见,输出摆幅接近电源电压(Vcc到GND)。幅度基本由Vc…时间:2026/02/13

有源晶振输出幅度怎么调整?

有源晶振输出幅度怎么调整?晶诺威科技解释如下: 有源晶振是完整的振荡器,其输出幅度主要由内部电路设计决定,在出厂时已固定。用户端的调整空间有限,且主要是衰减而非增强。 有源晶振的输出类型是选型时就必须确定的,它直接决定了幅度: CMOS:最常见,输出摆幅接近电源电压(Vcc到GND)。幅度基本由Vc…时间:2026/02/13 -

; ) 晶振输出波形有尖峰是什么原因?

关于晶振输出波形有尖峰问题,晶诺威科技解释如下: “晶振波形有尖峰”是一个常见问题,通常表明电路存在振铃、过冲或噪声干扰。这可能会影响时钟信号的稳定性和系统的可靠性。可能的原因及解决方案如下: 1、 阻抗匹配不当 晶振电路的走线太长或阻抗不匹配,导致信号反射,在上升沿/下降沿形成尖峰(振铃)。 建议…时间:2026/01/29

晶振输出波形有尖峰是什么原因?

关于晶振输出波形有尖峰问题,晶诺威科技解释如下: “晶振波形有尖峰”是一个常见问题,通常表明电路存在振铃、过冲或噪声干扰。这可能会影响时钟信号的稳定性和系统的可靠性。可能的原因及解决方案如下: 1、 阻抗匹配不当 晶振电路的走线太长或阻抗不匹配,导致信号反射,在上升沿/下降沿形成尖峰(振铃)。 建议…时间:2026/01/29 -

; ) CMOS输出的晶振能直接连接LVTTL逻辑吗?

CMOS输出的晶振能接LVTTL逻辑吗? 可以,但通常需要串联一个电阻。 一、电平标准回顾 CMOS输出晶振: 通常指输出电平符合CMOS逻辑标准的晶振。对于3.3V供电的晶振,其输出高电平(Voh)非常接近3.3V,低电平(Vol)非常接近0V。它的输出驱动能力较强,边沿非常陡峭。 LVTTL输入…时间:2025/11/08

CMOS输出的晶振能直接连接LVTTL逻辑吗?

CMOS输出的晶振能接LVTTL逻辑吗? 可以,但通常需要串联一个电阻。 一、电平标准回顾 CMOS输出晶振: 通常指输出电平符合CMOS逻辑标准的晶振。对于3.3V供电的晶振,其输出高电平(Voh)非常接近3.3V,低电平(Vol)非常接近0V。它的输出驱动能力较强,边沿非常陡峭。 LVTTL输入…时间:2025/11/08 -

; ) 无源晶振改有源晶振后,原芯片输出脚要接什么?

无源晶振改有源晶振后,原芯片输出脚要接什么? 答:XTAL_OUT(原输出脚)悬空或接地。 解释如下: 关于悬空还是接地处理,具体取决于芯片要求: 1、部分芯片要求此脚悬空(如STM32的OSC_OUT)。 2、某些设计可能需要通过一个小电容(如10pF)接地,以降低噪声干扰。 原芯片晶振输入引脚的…时间:2025/08/06

无源晶振改有源晶振后,原芯片输出脚要接什么?

无源晶振改有源晶振后,原芯片输出脚要接什么? 答:XTAL_OUT(原输出脚)悬空或接地。 解释如下: 关于悬空还是接地处理,具体取决于芯片要求: 1、部分芯片要求此脚悬空(如STM32的OSC_OUT)。 2、某些设计可能需要通过一个小电容(如10pF)接地,以降低噪声干扰。 原芯片晶振输入引脚的…时间:2025/08/06 -

; ) 有源晶振需要串联电阻吗?

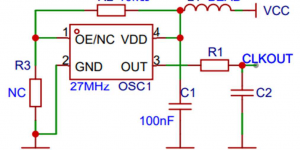

有源晶振需要串联电阻吗? 答:在有源晶振应用电路中,一般不需要串联电阻。 如上图所示: 当发生信号反射或/及信号完整性受损时,可以尝试增加一个低阻值串联电阻,选值一般为几十欧姆,如20~50欧姆。时间:2024/09/05

有源晶振需要串联电阻吗?

有源晶振需要串联电阻吗? 答:在有源晶振应用电路中,一般不需要串联电阻。 如上图所示: 当发生信号反射或/及信号完整性受损时,可以尝试增加一个低阻值串联电阻,选值一般为几十欧姆,如20~50欧姆。时间:2024/09/05 -

; ) 石英晶体振荡器(OSC)及其周围电路噪声(noise)发生源分析

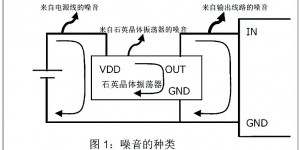

关于石英晶体振荡器(OSC)及其周围电路噪声(noise)发生源问题,晶诺威科技分析如下: 一般情况下,在石英晶体振荡器提供时钟信号的电路中,噪声(noise)发生源分为三大类:输出线路、电源线及石英晶体振荡器(oscillator)。 解释: 1、来自输出线路的噪声 来自输出线路的噪声是指输出线路…时间:2024/05/09

石英晶体振荡器(OSC)及其周围电路噪声(noise)发生源分析

关于石英晶体振荡器(OSC)及其周围电路噪声(noise)发生源问题,晶诺威科技分析如下: 一般情况下,在石英晶体振荡器提供时钟信号的电路中,噪声(noise)发生源分为三大类:输出线路、电源线及石英晶体振荡器(oscillator)。 解释: 1、来自输出线路的噪声 来自输出线路的噪声是指输出线路…时间:2024/05/09 -

; ) 数字电路中信号异常及可能原因

关于数字电路中信号异常及可能原因,晶诺威科技归纳如下: 1、幅值异常 波形不稳定,导致无法判定高低电平。 可能原因: 负载太大 走线过长 驱动太小 电平异常 2、过冲/回冲 方波过冲/回冲过高。超出正常电平10%。 可能原因: 驱动过高 存在反射 自激振荡 检查去耦 避免晶体振荡器输出波形失真的对策…时间:2023/12/13

数字电路中信号异常及可能原因

关于数字电路中信号异常及可能原因,晶诺威科技归纳如下: 1、幅值异常 波形不稳定,导致无法判定高低电平。 可能原因: 负载太大 走线过长 驱动太小 电平异常 2、过冲/回冲 方波过冲/回冲过高。超出正常电平10%。 可能原因: 驱动过高 存在反射 自激振荡 检查去耦 避免晶体振荡器输出波形失真的对策…时间:2023/12/13 -

; ) 有源晶振需要加负载电容吗?

有源晶振需要加负载电容吗? 答:一般情况下,有源晶振应用电路中不需要加负载电容。 注:常规有源晶振内部石英晶体的负载电容为15pF,也有少数有源晶振为30pF或50pF。 举例:有源晶振应用电路范例如下: 注:若#1无需其使能(EN)功能,可悬空处理。 在有源晶振应用电路中,内部振荡电路已经完成最佳…时间:2023/12/12

有源晶振需要加负载电容吗?

有源晶振需要加负载电容吗? 答:一般情况下,有源晶振应用电路中不需要加负载电容。 注:常规有源晶振内部石英晶体的负载电容为15pF,也有少数有源晶振为30pF或50pF。 举例:有源晶振应用电路范例如下: 注:若#1无需其使能(EN)功能,可悬空处理。 在有源晶振应用电路中,内部振荡电路已经完成最佳…时间:2023/12/12