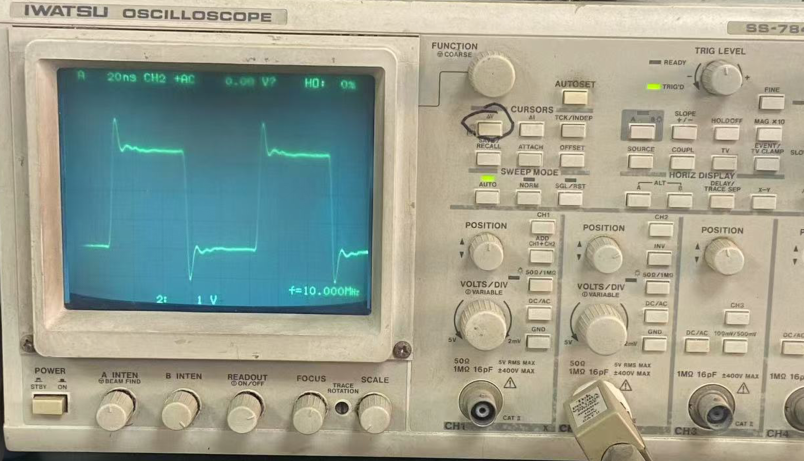

关于晶振输出波形有尖峰问题,晶诺威科技解释如下:

“晶振波形有尖峰”是一个常见问题,通常表明电路存在振铃、过冲或噪声干扰。这可能会影响时钟信号的稳定性和系统的可靠性。可能的原因及解决方案如下:

1、 阻抗匹配不当

晶振电路的走线太长或阻抗不匹配,导致信号反射,在上升沿/下降沿形成尖峰(振铃)。

建议:

- 尽量缩短晶振到芯片的走线,并使其靠近主芯片。

- 在信号线上串联一个小电阻(如10-100Ω) 来阻尼振荡,通常放在晶振输出脚和芯片输入脚之间。

2、 电源噪声

电源不稳定或噪声较大,通过电源引脚耦合到晶振电路。

建议:

- 为晶振的电源引脚增加去耦电容(如10nF + 100pF组合),并尽量靠近芯片电源引脚。

- 检查电源平面是否稳定,必要时为晶振部分使用LC滤波。

3、 测量方法引入的干扰

示波器探头的地线过长或接触不良,会引入寄生电感和噪声。

建议:

- 使用短地线(如探头接地弹簧),尽量减小测量回路面积。

- 将探头设置为10×档(阻抗更高,对电路影响更小)。

4、 负载电容不匹配

晶振的负载电容(CL)与电路设计不匹配,导致振荡不稳定。

建议:

- 根据晶振规格书调整负载电容(通常为两个贴片电容接地)。

- 典型值一般为10-22pF,需根据晶振和PCB寄生电容计算。

5、 电路布局不合理

晶振走线靠近高频或噪声源(如开关电源、射频电路)。

建议:

- 将晶振远离噪声源,并在周围铺地屏蔽。

- 避免在晶振下方或附近走其他信号线。

6、 晶振本身或驱动电路问题

晶振质量不佳,或芯片内部振荡器驱动能力过强。

建议:

- 尝试更换另一品牌/批次的晶振。

- 某些MCU允许调整晶振驱动强度(在配置寄存器中设为低驱动模式)。

调试建议

1、 先检查电源:用示波器查看晶振电源引脚是否有噪声。

2、 优化测量:确保探头接触良好并使用短地线。

3、 逐步调整:从串联电阻和调整负载电容开始,观察波形变化。