-

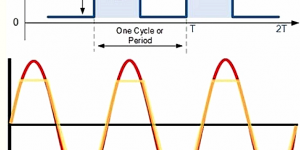

; ) 有源晶振方波输出与无源晶振正弦波输出对比

有源晶振方波输出与无源晶振正弦波输出对比如下: 方波主要用于数字通信系统的时钟,用来驱动纯计数电路或门电路。 方波主要有输出电平、占空比、上升/下降时间及驱动能力等几个指标要求。 正弦波主要用于对EMI和频率干扰有特殊要求的电路,这类电路要求输出的高次谐波分量很小。 模拟电路(如雷达、收音机等)设备…时间:2022/06/20

有源晶振方波输出与无源晶振正弦波输出对比

有源晶振方波输出与无源晶振正弦波输出对比如下: 方波主要用于数字通信系统的时钟,用来驱动纯计数电路或门电路。 方波主要有输出电平、占空比、上升/下降时间及驱动能力等几个指标要求。 正弦波主要用于对EMI和频率干扰有特殊要求的电路,这类电路要求输出的高次谐波分量很小。 模拟电路(如雷达、收音机等)设备…时间:2022/06/20 -

; ) 晶振输出波形:CMOS,LVPECL和LVDS

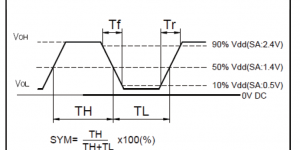

在数字电路中,我们需要选择晶振输出波形以匹配振荡器将在系统中驱动的负载。最常见的输出之一是CMOS,即以驱动逻辑电平输入。CMOS输出将是在地电位和系统的Vdd轨之间摆动的方波。对于高于约100MHz的较高频率,通常使用差分方波。 具备差分方波输出的振荡器具有两个180°异相的输出、具有快速上升和下…时间:2022/05/12

晶振输出波形:CMOS,LVPECL和LVDS

在数字电路中,我们需要选择晶振输出波形以匹配振荡器将在系统中驱动的负载。最常见的输出之一是CMOS,即以驱动逻辑电平输入。CMOS输出将是在地电位和系统的Vdd轨之间摆动的方波。对于高于约100MHz的较高频率,通常使用差分方波。 具备差分方波输出的振荡器具有两个180°异相的输出、具有快速上升和下…时间:2022/05/12 -

; ) CMOS,LVDS,HCSL,LV-PECL测试电路及时钟时序图

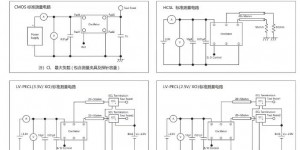

CMOS,LVDS,HCSL,LV-PECL测试电路及时钟时序图 由于在有源晶振内部加了整形电路,所以输出是方波,正弦波一般用的很少,普遍用的都是方波输出(很多时候在示波器上看到的还是波形不太好的正弦波,这是由于示波器的带宽不够。 例如:有源晶振20MHz,如果用40MHz或60MHz的示波器测量,…时间:2021/11/29

CMOS,LVDS,HCSL,LV-PECL测试电路及时钟时序图

CMOS,LVDS,HCSL,LV-PECL测试电路及时钟时序图 由于在有源晶振内部加了整形电路,所以输出是方波,正弦波一般用的很少,普遍用的都是方波输出(很多时候在示波器上看到的还是波形不太好的正弦波,这是由于示波器的带宽不够。 例如:有源晶振20MHz,如果用40MHz或60MHz的示波器测量,…时间:2021/11/29 -

; ) 晶诺威科技关于晶振指标,规格及参数详细说明

晶诺威科技关于晶振指标,规格及参数详细说明如下: 总频差:在规定的时间内,由于规定的工作和非工作参数全部组合而引起的晶体振荡器频率与给定标称频率的最大偏差。 说明:总频差包括频率温度稳定度、频率老化率造成的偏差、频率电压特性和频率负载特性等共同造成的最大频差。一般只在对短期频率稳定度关心,而对其他频…时间:2021/09/18

晶诺威科技关于晶振指标,规格及参数详细说明

晶诺威科技关于晶振指标,规格及参数详细说明如下: 总频差:在规定的时间内,由于规定的工作和非工作参数全部组合而引起的晶体振荡器频率与给定标称频率的最大偏差。 说明:总频差包括频率温度稳定度、频率老化率造成的偏差、频率电压特性和频率负载特性等共同造成的最大频差。一般只在对短期频率稳定度关心,而对其他频…时间:2021/09/18 -

; ) 无源晶振与有源晶振晶振主要输出波形对比

无源晶振与有源晶振晶振主要的输出波形对比如下: 1、无源晶振输出波形为:Sine Wave(正弦波) 2、常规OSC有源晶振输出波形为方波(CMOS):包括HCMOS、LVCMOS等。HCMOS(H:High,是“高”的意思)指3.3V及以上,LVCMOS(LV:Low Voltage…时间:2021/09/09

无源晶振与有源晶振晶振主要输出波形对比

无源晶振与有源晶振晶振主要的输出波形对比如下: 1、无源晶振输出波形为:Sine Wave(正弦波) 2、常规OSC有源晶振输出波形为方波(CMOS):包括HCMOS、LVCMOS等。HCMOS(H:High,是“高”的意思)指3.3V及以上,LVCMOS(LV:Low Voltage…时间:2021/09/09 -

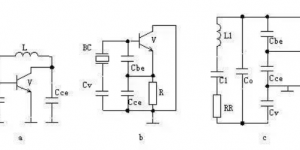

; ) 如何通过终端电阻对晶振输出波形output waveform进行整形?

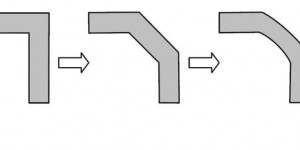

关于通过终端电阻对晶振输出波形output waveform进行整形方法,晶诺威科技介绍如下: 终端电阻的接法主要分为以下两种: 连接滤波器 通常可以使用串联电阻或终端电阻对输岀波形进行整形。若由此仍然无法完全解決问题,则使用滤波器。使用滤波器可去除高频率的相噪,但tr、tf将变大(脉冲前后沿变圆)…时间:2021/09/03

如何通过终端电阻对晶振输出波形output waveform进行整形?

关于通过终端电阻对晶振输出波形output waveform进行整形方法,晶诺威科技介绍如下: 终端电阻的接法主要分为以下两种: 连接滤波器 通常可以使用串联电阻或终端电阻对输岀波形进行整形。若由此仍然无法完全解決问题,则使用滤波器。使用滤波器可去除高频率的相噪,但tr、tf将变大(脉冲前后沿变圆)…时间:2021/09/03 -

; ) 关于无源晶振输出波形振幅不足导致系统异常问题

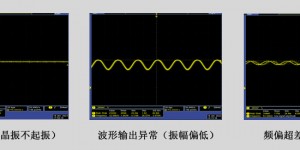

关于无源晶振输出波形振幅不足导致系统异常问题分析如下: 在晶振实际应用中,即使测得无源晶振输出频率几乎接近于目标频率,但若波形幅度不足,同样会影响系统正常工作。 晶诺威科技建议如下: 尝试降低外接电容值,采用负载电容(CL)较低的晶振。 尝试采用电阻较低的晶体(Rr)。 尝试使用不等值的外接电容设计…时间:2021/08/26

关于无源晶振输出波形振幅不足导致系统异常问题

关于无源晶振输出波形振幅不足导致系统异常问题分析如下: 在晶振实际应用中,即使测得无源晶振输出频率几乎接近于目标频率,但若波形幅度不足,同样会影响系统正常工作。 晶诺威科技建议如下: 尝试降低外接电容值,采用负载电容(CL)较低的晶振。 尝试采用电阻较低的晶体(Rr)。 尝试使用不等值的外接电容设计…时间:2021/08/26 -

; ) 有源晶振输出方式解析:CMOS,LVCMOS,TTL,LVTTL,LVDS

有源晶振常见输出方式(output waveform)图例 有源晶振常见输出方式(Output Waveform)如下: CMOS CMOS是Complementary Metal Oxide Semiconductor的英文缩写,这种接口电平标准的初衷是用于基于NMOS、PMOS组成的MOS管结构…时间:2021/08/25

有源晶振输出方式解析:CMOS,LVCMOS,TTL,LVTTL,LVDS

有源晶振常见输出方式(output waveform)图例 有源晶振常见输出方式(Output Waveform)如下: CMOS CMOS是Complementary Metal Oxide Semiconductor的英文缩写,这种接口电平标准的初衷是用于基于NMOS、PMOS组成的MOS管结构…时间:2021/08/25 -

; ) 差分晶振156.25MHz LVDS规格书及使用说明

差分晶振156.25MHz LVDS规格书及使用说明如下: PRODUCT TYPE(产品类型): SMD LVDS OSC DIMENSIONS(尺寸)3.2mm*2.5mm NOMINAL FREQ.(标称频率): 156.25MHz ELECTRICAL SPECIFICATIONS(差分晶振…时间:2021/08/20

差分晶振156.25MHz LVDS规格书及使用说明

差分晶振156.25MHz LVDS规格书及使用说明如下: PRODUCT TYPE(产品类型): SMD LVDS OSC DIMENSIONS(尺寸)3.2mm*2.5mm NOMINAL FREQ.(标称频率): 156.25MHz ELECTRICAL SPECIFICATIONS(差分晶振…时间:2021/08/20 -

; ) 为何测试无源晶振频率输出脚与频率输入脚频率或波形不一样

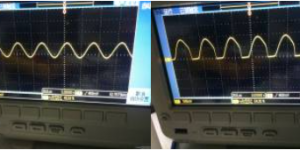

(32.768KHz无源晶振频率输出脚与频率输入脚实测频率或波形不一样范例) 如上图所示,测试无源晶振频率输出脚与频率输入脚频率或波形不一样,属于正常现象,因为一个是经由放大器的输出,振幅比较大。另外一个是放大器的输入,信号由输出端经晶振过来,振幅减弱,比较小。另外,测试仪表的探针电容大小、频宽差异…时间:2021/08/12

为何测试无源晶振频率输出脚与频率输入脚频率或波形不一样

(32.768KHz无源晶振频率输出脚与频率输入脚实测频率或波形不一样范例) 如上图所示,测试无源晶振频率输出脚与频率输入脚频率或波形不一样,属于正常现象,因为一个是经由放大器的输出,振幅比较大。另外一个是放大器的输入,信号由输出端经晶振过来,振幅减弱,比较小。另外,测试仪表的探针电容大小、频宽差异…时间:2021/08/12