-

; ) RTC晶振32.768KHz负载电容CL选用12.5pF还是7pF?

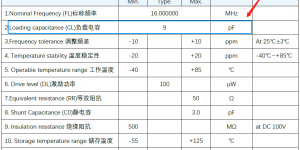

RTC晶振32.768KHz负载电容CL选用12.5pF还是7pF? 答:RTC晶振负载电容CL大小由芯片决定,请根据芯片数据手册取值。若无源晶振的负载电容CL选择错误,可能造成晶振不起振。 RTC晶振32.768KHz负载电容CL值常见有:7pF、9pF、12.5pF等,不同负载电容CL应匹配不同…时间:2025/12/25

RTC晶振32.768KHz负载电容CL选用12.5pF还是7pF?

RTC晶振32.768KHz负载电容CL选用12.5pF还是7pF? 答:RTC晶振负载电容CL大小由芯片决定,请根据芯片数据手册取值。若无源晶振的负载电容CL选择错误,可能造成晶振不起振。 RTC晶振32.768KHz负载电容CL值常见有:7pF、9pF、12.5pF等,不同负载电容CL应匹配不同…时间:2025/12/25 -

; ) 贴错电容导致32.768KHz晶振无法起振引发系统无法正常启动案例分析

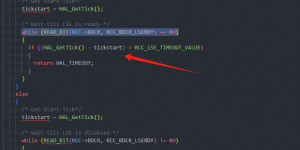

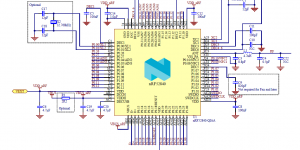

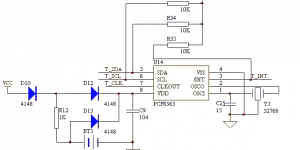

(LSE TIMEOUT) 一、 现象描述 现象:板子烧录完程序,无法启动。此时有多种可能导致系统正常启动: 1. 烧录方面:没烧录boot或app、烧录导致内部flash锁死 2. 硬件方面:硬件的供电系统、晶振无法正常起振、复位电路正常、板子是否存在虚焊或短接问题、内部flash损坏(低概率) …时间:2025/10/21

贴错电容导致32.768KHz晶振无法起振引发系统无法正常启动案例分析

(LSE TIMEOUT) 一、 现象描述 现象:板子烧录完程序,无法启动。此时有多种可能导致系统正常启动: 1. 烧录方面:没烧录boot或app、烧录导致内部flash锁死 2. 硬件方面:硬件的供电系统、晶振无法正常起振、复位电路正常、板子是否存在虚焊或短接问题、内部flash损坏(低概率) …时间:2025/10/21 -

; ) 晶振的匹配电容太小会怎样?

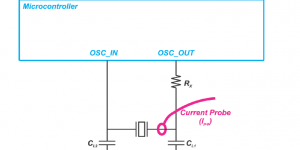

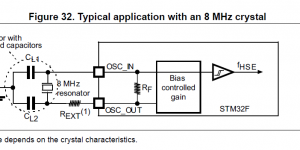

晶振的匹配电容太小会怎样? 答:在无源晶体谐振器电路应用中,若外接的匹配电容(CL1和CL2)太小的话,可能导致其输出频率偏离中心点,偏离方向为正向。 举例: 若晶振中心频率为8.000000MHz,本身负载电容(CL=18pF),应匹配27pF左右,如果选取12pF外接电容,可能导致其实际输出频率…时间:2025/06/20

晶振的匹配电容太小会怎样?

晶振的匹配电容太小会怎样? 答:在无源晶体谐振器电路应用中,若外接的匹配电容(CL1和CL2)太小的话,可能导致其输出频率偏离中心点,偏离方向为正向。 举例: 若晶振中心频率为8.000000MHz,本身负载电容(CL=18pF),应匹配27pF左右,如果选取12pF外接电容,可能导致其实际输出频率…时间:2025/06/20 -

; ) 晶振的起振电容太大了会有什么影响?

晶振的起振电容太大了会有什么影响? 答:会造成晶振频率偏负向、起振慢甚至停振。 晶诺威科技进一步解释如下: 晶振的起振电容(外接电容,通常为CL1和CL2)过大会对电路产生以下影响: 1、 频率偏移 起振电容过大会导致晶振输出频率低于标称频率。对时序敏感的电路(如MCU、通信模块),频率偏差可能导致…时间:2025/06/10

晶振的起振电容太大了会有什么影响?

晶振的起振电容太大了会有什么影响? 答:会造成晶振频率偏负向、起振慢甚至停振。 晶诺威科技进一步解释如下: 晶振的起振电容(外接电容,通常为CL1和CL2)过大会对电路产生以下影响: 1、 频率偏移 起振电容过大会导致晶振输出频率低于标称频率。对时序敏感的电路(如MCU、通信模块),频率偏差可能导致…时间:2025/06/10 -

; ) 晶振匹配电容过小会正偏吗?

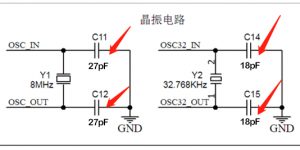

晶振匹配电容过小会正偏吗? 答:是的。晶振匹配电容过小,会导致频率偏正。 (32.768KHz晶振与32MHz晶振应用电路图例) 如果发生晶振输出频率偏正向(大)的现象,请增大外接匹配电容。举例:如果外接电容为12PF,请尝试调至15pF、18pF或22pF。关于两颗外接电容,建议等值调整,以确保晶…时间:2025/02/22

晶振匹配电容过小会正偏吗?

晶振匹配电容过小会正偏吗? 答:是的。晶振匹配电容过小,会导致频率偏正。 (32.768KHz晶振与32MHz晶振应用电路图例) 如果发生晶振输出频率偏正向(大)的现象,请增大外接匹配电容。举例:如果外接电容为12PF,请尝试调至15pF、18pF或22pF。关于两颗外接电容,建议等值调整,以确保晶…时间:2025/02/22 -

; ) 晶体的负载电容会影响起振吗?

晶体的负载电容会影响起振吗? 答:会的。若晶体的负载电容选择错误,可能导致晶体频偏、起振慢或不起振等问题。 晶诺威科技建议: 关于晶体的负载电容选择,请参照芯片手册及晶振供应商给出的最佳匹配电容参考值。时间:2025/01/21

晶体的负载电容会影响起振吗?

晶体的负载电容会影响起振吗? 答:会的。若晶体的负载电容选择错误,可能导致晶体频偏、起振慢或不起振等问题。 晶诺威科技建议: 关于晶体的负载电容选择,请参照芯片手册及晶振供应商给出的最佳匹配电容参考值。时间:2025/01/21 -

; ) 9pF和12pF负载电容的晶振有什么区别?

9pF和12pF负载电容的晶振有什么区别? 答:晶振负载电容(CL)的大小一般是由芯片方案决定。 如果晶振负载电容(CL)选择错误,可能会导致晶振时钟电路不稳定或故障,具体表现为晶振起振时间延长、频率稳定性降低、频率精度误差增加、波形幅值不够等诸多问题。因此,如果芯片手册指定晶振负载电容(CL)为9…时间:2025/01/18

9pF和12pF负载电容的晶振有什么区别?

9pF和12pF负载电容的晶振有什么区别? 答:晶振负载电容(CL)的大小一般是由芯片方案决定。 如果晶振负载电容(CL)选择错误,可能会导致晶振时钟电路不稳定或故障,具体表现为晶振起振时间延长、频率稳定性降低、频率精度误差增加、波形幅值不够等诸多问题。因此,如果芯片手册指定晶振负载电容(CL)为9…时间:2025/01/18 -

; ) Crystal 12MHz and 25MHz for W5500-EVB-Pico

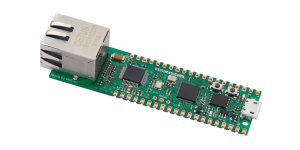

W5500-EVB-Pico Crystal 12MHz and 25MHz for W5500-EVB-Pico W5500-EVB-Pico is a microcontroller evaluation board based on the Raspberry Pi RP2040 and fu…时间:2024/12/31

Crystal 12MHz and 25MHz for W5500-EVB-Pico

W5500-EVB-Pico Crystal 12MHz and 25MHz for W5500-EVB-Pico W5500-EVB-Pico is a microcontroller evaluation board based on the Raspberry Pi RP2040 and fu…时间:2024/12/31 -

; ) 晶振外接负载电容范围一般是多少pF?

晶振外接负载电容范围一般是多少pF? 答:外接负载电容通常指的是无源晶振的两个匹配电容,其选值范围分别为6pF~33pF。一般等值选取。 注: 如果外接电容选择错误,可能造成晶振起振困难、不起振或频偏超差。因此,在常见的无源晶振应用电路中,匹配电容的选取非常关键。时间:2024/09/23

晶振外接负载电容范围一般是多少pF?

晶振外接负载电容范围一般是多少pF? 答:外接负载电容通常指的是无源晶振的两个匹配电容,其选值范围分别为6pF~33pF。一般等值选取。 注: 如果外接电容选择错误,可能造成晶振起振困难、不起振或频偏超差。因此,在常见的无源晶振应用电路中,匹配电容的选取非常关键。时间:2024/09/23 -

; ) 芯片对晶振外接匹配电容的配置要求

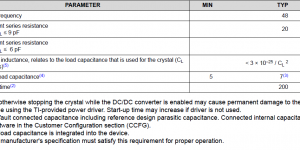

(该芯片推荐晶振负载电容为:最小值5pF,典型值7pF,最大值9pF) 关于芯片对晶振外接匹配电容的配置要求,需要仔细阅读芯片手册相关内容。 举例:某款芯片对晶振外接电容配置说明如下: On-chip default connected capacitance including reference…时间:2024/09/09

芯片对晶振外接匹配电容的配置要求

(该芯片推荐晶振负载电容为:最小值5pF,典型值7pF,最大值9pF) 关于芯片对晶振外接匹配电容的配置要求,需要仔细阅读芯片手册相关内容。 举例:某款芯片对晶振外接电容配置说明如下: On-chip default connected capacitance including reference…时间:2024/09/09