晶振接数字地还是模拟地?

答:以接数字地为主,如下:

1、大多数数字系统:接数字地,确保低噪声电源和紧凑布局;

2、混合信号系统:接数字地,单点连接模拟地,重点关注回流路径;

3、高频/精密模拟:评估噪声敏感性,可能需接模拟地或隔离处理。

在电路设计中,晶振的接地处理需根据具体应用和系统架构决定。以下是关键考虑因素和建议:

1、 晶振类型决定接地方式

无源晶振(需外部电路):

通常建议接数字地,因为其驱动电路(如MCU的振荡器)属于数字范畴。高频噪声可能通过地平面耦合,需确保数字地干净。

有源晶振(自带振荡电路):

若为数字系统提供时钟,接数字地;若用于模拟电路(如射频、ADC),需评估是否接模拟地或通过磁珠/电容隔离。

2、 混合信号系统的处理

单点接地策略:

若系统同时存在数字地和模拟地,晶振(尤其是高速晶振)应接数字地,并在电源入口处通过0Ω电阻或磁珠将数字地与模拟地单点连接,避免地环路噪声。

分割地平面的注意事项:

高频晶振(如>10MHz)的回流路径需完整,地平面分割可能导致阻抗不连续,反而增加辐射。此时可优先保持完整地平面,通过布局隔离而非分割。

3、 降低噪声的关键措施

局部去耦:

在晶振电源引脚就近放置0.1μF+10pF电容组合,形成低阻抗回路,高频噪声直接回流到地而非耦合到其他部分。

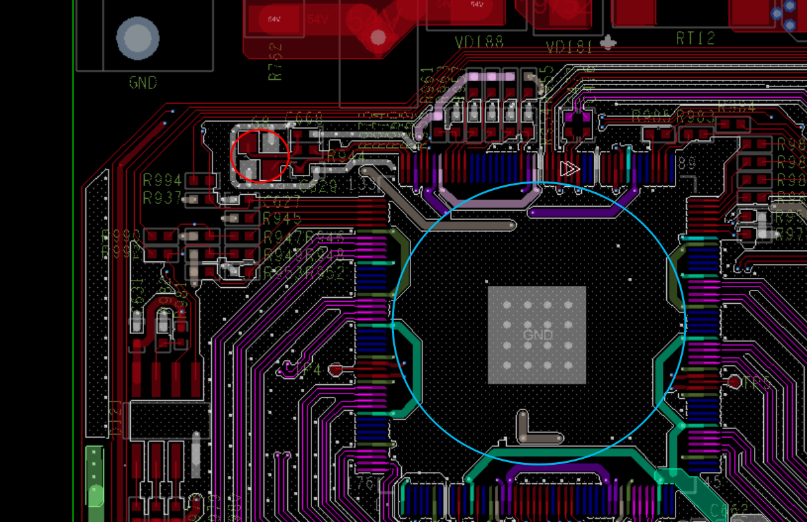

短路径布线:

晶振走线尽量短,且下方保持完整地平面,避免跨分割区。时钟信号远离模拟敏感线路。

屏蔽(必要时):

对高频或敏感电路,可用金属屏蔽罩覆盖晶振并接地,进一步抑制辐射。

4、 特殊场景建议

高频/射频系统:

若晶振用于射频本振,需严格接模拟地,并采用独立电源滤波,避免相位噪声恶化。

多时钟系统:

不同晶振的地可通过局部星型连接汇聚到主接地点,减少相互干扰。