-

; ) 晶振接数字地还是模拟地?

晶振接数字地还是模拟地? 答:以接数字地为主,如下: 1、大多数数字系统:接数字地,确保低噪声电源和紧凑布局; 2、混合信号系统:接数字地,单点连接模拟地,重点关注回流路径; 3、高频/精密模拟:评估噪声敏感性,可能需接模拟地或隔离处理。 在电路设计中,晶振的接地处理需根据具体应用和系统架构决定。以…时间:2025/07/23

晶振接数字地还是模拟地?

晶振接数字地还是模拟地? 答:以接数字地为主,如下: 1、大多数数字系统:接数字地,确保低噪声电源和紧凑布局; 2、混合信号系统:接数字地,单点连接模拟地,重点关注回流路径; 3、高频/精密模拟:评估噪声敏感性,可能需接模拟地或隔离处理。 在电路设计中,晶振的接地处理需根据具体应用和系统架构决定。以…时间:2025/07/23 -

; ) 晶振频率变化快是什么原因?

晶振频率变化快是什么原因? 答:晶振频率变化快主要是由频率不稳定所导致。 关于导致晶振频率变化快(频率不稳定)的可能性因素,常见原因如下: 1、 晶振频率对温度敏感,尤其是无温度补偿的普通晶振。温度快速波动会导致频率漂移。 建议:保持环境温度稳定,避免热源干扰。 2、 电源噪声或电压不稳会影响晶振的…时间:2025/06/18

晶振频率变化快是什么原因?

晶振频率变化快是什么原因? 答:晶振频率变化快主要是由频率不稳定所导致。 关于导致晶振频率变化快(频率不稳定)的可能性因素,常见原因如下: 1、 晶振频率对温度敏感,尤其是无温度补偿的普通晶振。温度快速波动会导致频率漂移。 建议:保持环境温度稳定,避免热源干扰。 2、 电源噪声或电压不稳会影响晶振的…时间:2025/06/18 -

; ) 关于无源晶振起振与停振现象的解释

关于无源晶振起振与停振现象,晶诺威科技解释如下: 无源晶振(晶体谐振器)的起振与停振是电路设计中需要重点关注的现象,以下是详细分析: 一、 晶振起振过程 1. 起振条件 环路增益 ≥1:振荡电路的放大环节(如反相器、晶体管)需提供足够增益,补偿晶振和电路的损耗。 相位匹配:环路总相位偏移必须为360…时间:2025/05/26

关于无源晶振起振与停振现象的解释

关于无源晶振起振与停振现象,晶诺威科技解释如下: 无源晶振(晶体谐振器)的起振与停振是电路设计中需要重点关注的现象,以下是详细分析: 一、 晶振起振过程 1. 起振条件 环路增益 ≥1:振荡电路的放大环节(如反相器、晶体管)需提供足够增益,补偿晶振和电路的损耗。 相位匹配:环路总相位偏移必须为360…时间:2025/05/26 -

; ) PCBA板喷了三防漆晶振不起振原因分析

关于PCBA板喷了三防漆晶振不起振原因,晶诺威科技分析如下: 当电路板喷涂三防漆后出现晶振不起振的问题,可能是由于漆层影响了晶振电路的正常工作。以下是逐步排查和解决方案: 1、 检查三防漆的材质影响 介电常数问题:某些三防漆的介电常数较高,可能导致晶振负载电容变化,偏离设计值。 解决:选择低介电常数…时间:2025/05/06

PCBA板喷了三防漆晶振不起振原因分析

关于PCBA板喷了三防漆晶振不起振原因,晶诺威科技分析如下: 当电路板喷涂三防漆后出现晶振不起振的问题,可能是由于漆层影响了晶振电路的正常工作。以下是逐步排查和解决方案: 1、 检查三防漆的材质影响 介电常数问题:某些三防漆的介电常数较高,可能导致晶振负载电容变化,偏离设计值。 解决:选择低介电常数…时间:2025/05/06 -

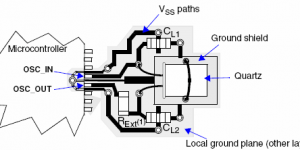

; ) 关于SMD3225晶振布线说明

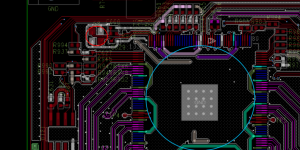

关于SMD3225晶振布线设计,晶诺威科技说明如下: SMD3225晶振是一种表面贴装(SMD)封装的石英晶体振荡器,尺寸为3.2mm × 2.5mm。它在高频电路中广泛应用,如通信设备、消费电子和工业控制等。为了确保SMD3225晶振的正常工作和稳定性,PCB布线设计非常关键。以下是SMD3225…时间:2025/04/18

关于SMD3225晶振布线说明

关于SMD3225晶振布线设计,晶诺威科技说明如下: SMD3225晶振是一种表面贴装(SMD)封装的石英晶体振荡器,尺寸为3.2mm × 2.5mm。它在高频电路中广泛应用,如通信设备、消费电子和工业控制等。为了确保SMD3225晶振的正常工作和稳定性,PCB布线设计非常关键。以下是SMD3225…时间:2025/04/18 -

; ) 信号线到晶振的距离是多少?

信号线到晶振的距离是多少? 答:距离越短越好,通常不超过5厘米,高频应用需更短。 信号线到晶振的距离应尽可能短,以减少噪声和信号完整性问题。晶诺威科技具体建议如下: 一般建议: 距离最好控制在 5厘米 以内。 高频应用: 在高频电路中,距离应进一步缩短,通常小于 2.5厘米。 布局优化: 信号线应直…时间:2025/04/10

信号线到晶振的距离是多少?

信号线到晶振的距离是多少? 答:距离越短越好,通常不超过5厘米,高频应用需更短。 信号线到晶振的距离应尽可能短,以减少噪声和信号完整性问题。晶诺威科技具体建议如下: 一般建议: 距离最好控制在 5厘米 以内。 高频应用: 在高频电路中,距离应进一步缩短,通常小于 2.5厘米。 布局优化: 信号线应直…时间:2025/04/10 -

; ) How to place the crystal oscillator on the PCB?

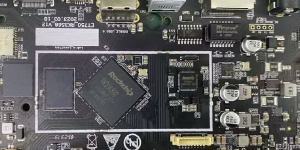

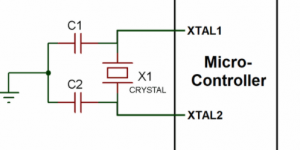

How to place the crystal oscillator on the PCB? Place the crystal oscillator as close as possible to the corresponding input and output pins of the ch…时间:2024/05/09

How to place the crystal oscillator on the PCB?

How to place the crystal oscillator on the PCB? Place the crystal oscillator as close as possible to the corresponding input and output pins of the ch…时间:2024/05/09 -

; ) Crystal Oscillator PCB Layout Guidelines for Design

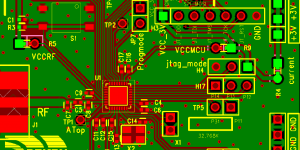

(Crystal Oscillator PCB Layout Guidelines for Design) When using a crystal oscillator in your PCB design, remember that it is very EMI sensitive and m…时间:2024/04/25

Crystal Oscillator PCB Layout Guidelines for Design

(Crystal Oscillator PCB Layout Guidelines for Design) When using a crystal oscillator in your PCB design, remember that it is very EMI sensitive and m…时间:2024/04/25 -

; ) Layout issues of crystal oscillators

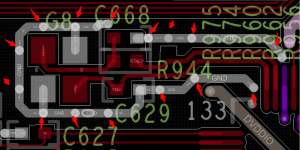

(Layout issues of crystal oscillators) Good layout practices are fundamental to the correct operation and reliability of the oscillator. It is critica…时间:2024/04/23

Layout issues of crystal oscillators

(Layout issues of crystal oscillators) Good layout practices are fundamental to the correct operation and reliability of the oscillator. It is critica…时间:2024/04/23 -

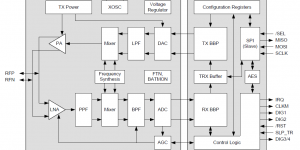

; ) 无线高数据速率模式下晶振选型及布线注意事项

关于无线高数据速率模式下晶振选型及布线注意事项,晶诺威科技解释如下: 无线信号传输设备(如:蓝牙、Wi-Fi、ZigBee、Lora等)内部产生的频率都来自晶振所提供的频率(如:16MHz)。因此可以说,整个无线系统的性能主要取决于晶振参考频率的精度及稳定性。 对晶体振荡器的外部元器件应慎重选择,相…时间:2024/03/14

无线高数据速率模式下晶振选型及布线注意事项

关于无线高数据速率模式下晶振选型及布线注意事项,晶诺威科技解释如下: 无线信号传输设备(如:蓝牙、Wi-Fi、ZigBee、Lora等)内部产生的频率都来自晶振所提供的频率(如:16MHz)。因此可以说,整个无线系统的性能主要取决于晶振参考频率的精度及稳定性。 对晶体振荡器的外部元器件应慎重选择,相…时间:2024/03/14