若40MHz晶振负载电容为8pF,外部电容选择多大?

答:推荐10pF~12pF。

晶体振荡器的负载电容 CL 由以下公式定义:

CL = (C1 × C2) / (C1 + C2) + Cstray

其中:

C1, C2:就是我们选择的外部两个电容,通常为了对称,取相同值。

Cstray:是电路的杂散电容。这包括晶振本身的管脚电容、MCU引脚的输入输出电容、PCB走线之间的寄生电容等。这个值通常在2pF到5pF之间,对于精确设计,需要参考MCU和晶振的数据手册,但在绝大多数普通双层板应用中,我们通常估算为3pF到5pF。

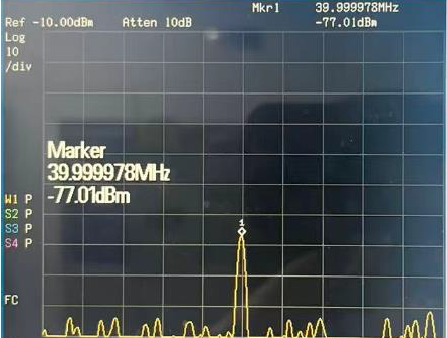

在批量生产前,最好用高精度频率计测量一下实际振荡频率。如果频率略微偏慢,说明负载电容偏大,可以适当减小 C1/C2;如果频率略微偏快,说明负载电容偏小,可以适当增大 C1/C2。

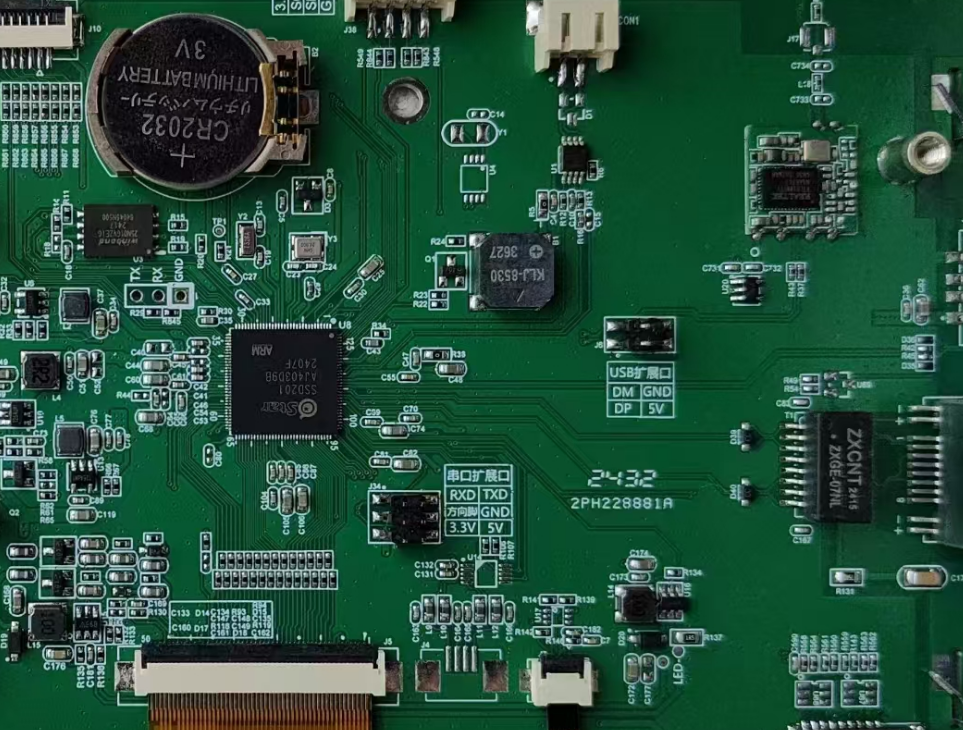

40MHz属于较高频率,通常为低功耗RF射频应用,PCB布局非常重要:晶振要紧靠MCU的振荡引脚,走线尽量短而粗,用地线包围进行隔离,远离噪声源和电源线。