(晶振辐射超标)

网口EMC辐射超标是硬件设计中非常经典的难题。它的根源往往是一个“干扰源”加上一条“发射天线”的组合——板上的高频噪声(比如晶振的谐波)通过网口这个路径,以共模电流的形式耦合到网线上,而网线本身就是一根高效的 antenna,将噪声辐射出去。

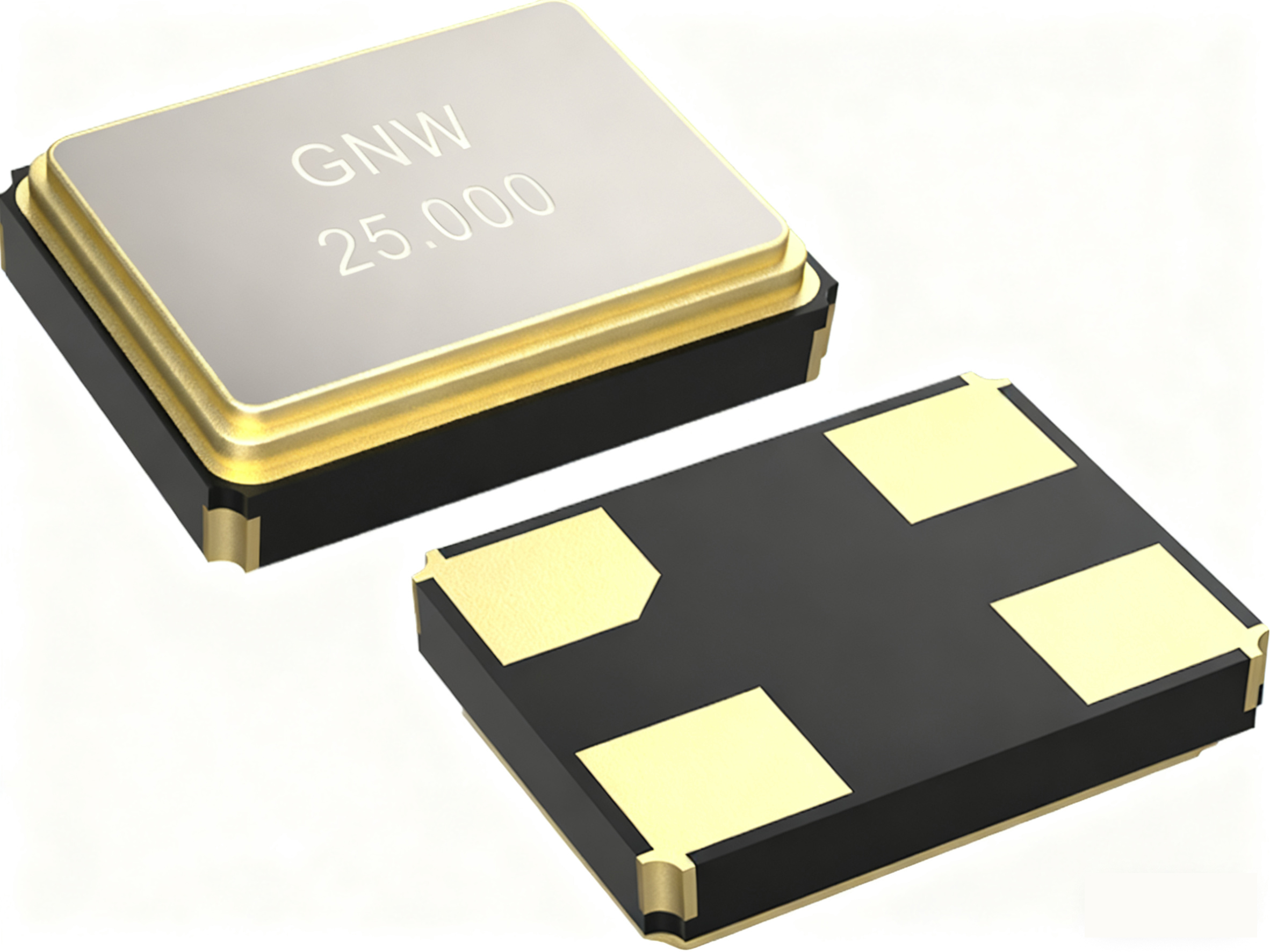

简单来说,网口晶振(如:25MHz/50MHz)辐射超标是一个非常经典且常见的EMC(电磁兼容)问题。晶振及其时钟电路是主板上的主要高频噪声源,而网口本身作为一个“天线”,很容易将这些噪声辐射出去,导致测试失败。

为什么网口晶振容易导致辐射超标?

1、 高频噪声源

晶振本身工作在高频,其产生的方波信号富含高频谐波。这些谐波的频率可以轻松延伸到几百MHz甚至GHz,正好落在EMC辐射测试的敏感频段(30MHz ~ 1GHz)。

2、 共模电流路径

这是最关键的原因。网口变压器(Network Transformer 或 MagJack)的中心抽头通过电容连接到机壳地(Chassis GND)。这个路径为晶振产生的高频噪声提供了一个“完美”的共模电流回路。

噪声耦合:晶振的噪声通过空间辐射或PCB走线耦合到网口相关的走线(尤其是晶振金属外壳和连接网线的屏蔽层)。

天线形成:网线本身是一根很好的天线。共模电流沿着网线流动,将噪声高效地辐射出去。

3、 糟糕的PCB布局:

![]() 晶振/时钟电路靠近网口:这是最直接的原因,路径短,耦合强。

晶振/时钟电路靠近网口:这是最直接的原因,路径短,耦合强。

![]() 信号回流路径不完整:时钟信号线的参考地平面不完整,有割裂,导致回流路径环路面积过大,形成磁环天线。

信号回流路径不完整:时钟信号线的参考地平面不完整,有割裂,导致回流路径环路面积过大,形成磁环天线。

![]() 电源去耦不足:晶振和主芯片的电源引脚缺少足够和合适的高频去耦电容。

电源去耦不足:晶振和主芯片的电源引脚缺少足够和合适的高频去耦电容。

解决方案与建议

一、优化网口变压器的共模滤波

在变压器中心抽头(Center Tap)连接到机壳地的电容路径上,串联一个共模扼流圈(Common Mode Choke)或一个高频磁珠(Ferrite Bead)。

目的:极大地增加共模电流路径上的高频阻抗,从而抑制共模电流流向网口这个“天线”。

注意:选择磁珠时,要看其在噪声频率范围内的阻抗曲线,阻抗越高越好。

加强网口屏蔽与接地:确保网口的金属外壳与设备的金属机壳实现低阻抗、360度的良好搭接。接触不良会使其本身成为一个辐射体。

如果机壳是塑料材质,那么网口金属外壳需要通过一个高频电容(如100pF)连接到主板的工作地(GND),为共模噪声提供一个低阻抗的回流路径。

二、对晶振本身进行屏蔽

在晶振上方加一个金属屏蔽罩,并将其与PCB地良好焊接。这是一种物理隔离方法。

PCB布局优化

1、 增加间距:在后续版本设计中,务必让晶振和所有高频时钟走线远离网口、连接器和板边。至少保持1cm以上的距离,越远越好。

2、 完整地平面:为时钟信号提供一个完整、无割裂的参考地平面。确保信号线下的回流路径是顺畅的,以减小环路面积。

3、 包地处理:用地线将晶振的时钟走线包围起来,并在地线上多次打过孔连接到主地平面。这可以起到一定的屏蔽和隔离作用。

4、 避免走线在分割区跨分割:严禁时钟信号线跨地平面或电源平面的分割区。

三、元器件选择与电路设计

1、 使用展频晶振(SSCG – Spread Spectrum Oscillator)

这是一种非常有效的方法。它通过将时钟能量的主峰展宽到一个较宽的频率范围内,从而降低峰值能量。

2、 串联阻尼电阻

在晶振的时钟输出脚上,串联一个小的电阻(如10~33Ω)。这个电阻与负载电容和走线寄生电容会形成一个低通滤波器,可以平滑时钟信号的边沿,减少高频谐波分量。

注意:电阻值不能太大,否则会影响时钟信号的建立时间,导致时序问题。

3、 优化去耦

在晶振的电源引脚和主芯片的时钟输入引脚附近,放置多种容值(如10uF, 0.1uF, 10pF)的去耦电容,以滤除不同频段的电源噪声。